The reduction of input open-fault in a CMOS Schmitt-Trigger inverter

DOI:

https://doi.org/10.55674/snrujst.v14i2.245040Keywords:

CMOS inverter, Self-oscillation, Open-fault, Fail-safeAbstract

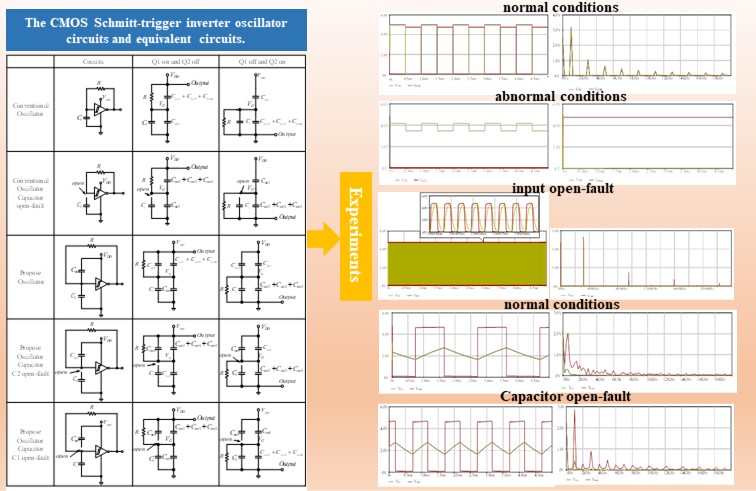

The failure of the CMOS Schmitt-trigger inverter open-fault and capacitor open-fault in the case of a CMOS Schmitt-trigger inverter oscillator circuit cause a self-oscillation of the device. It leads to the high frequency to be emitted on the output side, because the balance of internal smaller parasitic capacitance approximately 5 – 20 pF. In this article, the reduction of CMOS Schmitt-trigger inverter open-fault and capacitor open-fault in the case of a CMOS Schmitt-trigger inverter oscillator circuit is presented, by adding a capacitor between the Gate pin and Drain pin of Q1 by demonstration illusion of an equivalent circuit. This causes the internal parasitic capacitance to unbalance, then the self-oscillation in the case of input open-fault will not accord. Besides in the case of an oscillator circuit, the feedback resistor is not combined with the internal parasitic capacitance. However, it is combined it is with the added capacitance, the higher frequency self-oscillation does not occur. The circuit was tested with a PSPICE computer simulation program.

References

K. Otake, Y. Hirao, T. Fukuda, K. Futsuhara, A safety relay with contacts in a safe operational order and its application, 6th International Conference on Safety of Industrial Automated Systems (SIAS 2010), Safety of Industrial Automated Systems. 14 – 15 June 2010, 1 – 6.

S. Deeon, Y. Hirao, K. Tanaka, A relay drive circuit for a safe operation order and its fail-safe measures, J. Rel. Eng. Association of Japan. 34(7) (2012) 489 – 500.

S. Deeon, A. Pilikeaw, Anti self-oscillation of CMOS invertors ICs for a fail-safe relay drive circuit, Electrical Engineering Network of Rajamangala University of Technology 2015, Rajamangala University of Technology Krungthep. 25 – 27 May 2015, 428 – 431.

C. Summatta, S. Deeon, Simple anti capacitor open-circuit self-oscillation in a CMOS Schmitt Trigger-invertor oscillator circuit, Przeglad Elektrotechniczny. 95(3) (2019) 97 – 100.

R.J. Baker, CMOS: Circuit design, layout, and simulation, third Edition., John Wiley & Sons, New York, 2010.

V. Bobin, S. Whitaker, Design of fail-safe CMOS logic circuits, Great Lakes Symposium on VLSI, Institute of Electrical and Electronics Engineers (IEEE). 1 – 2 March 1991, 338 – 339.

Downloads

Published

How to Cite

Issue

Section

License

Copyright (c) 2022 SNRU Journal of Science and Technology

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.