Probabilistic Modelling of Variation in FGMOSFET

Main Article Content

Abstract

The analytical probabilistic modelling of random variation in the drain current of a Floating-Gate MOSFET (FGMOSFET) induced by manufacturing process variations has been performed. Both triode and saturation region operated FGMOSFETs have been considered. The results have been found to be very efficient since they can accurately fit the probabilistic distributions of normalized random drain current variations of the candidate triode and saturation FGMOSFETs obtained using the 0.25μm level BSIM3v3 based Monte-Carlo SPICE simulations, where the variation of the saturation FGMOSFET has been found to be more severe. These results also satisfy the goodness of fit test at a very high level of confidence and more accurately than the results of the previous probabilistic modelling attempts. Using our results, many statistical parameters, probabilities and the objective functions, which are useful in statistical/variability aware analysis and design involving FGMOSFETs can be formulated. The impact of drain current variation upon the design trade-offs can be studied. It has been found that the occurrence of the drain current variation is absolutely certain. Moreover, the analytical probabilistic modelling and computationally efficient statistical/ variability aware simulation of FGMOSFET based circuits can also be performed.

Article Details

References

G. Serrano, and P. Hasler, “A Floating Gate DAC Array,” Proceeding of the 2004 International Symposium on Circuits and Systems (IS-CAS 04), pp. 357-360, 2004.

M. Drakaki, G. Fikos and S. Siskos, “Analog Signal Processing Circuits Using Floating Gate MOS Transistors,” Proceedings of the International Conference on Technology and Automation (ICTA 05), pp. 322-327, 2005.

S. Sharma, S.S. Rajput, L.K. Mangotra and S.S. Jamuar, “Applications of A New FGMOS Based CCII in Low Voltage Analog Filters,” Indian Journal of Engineering and Materials Sciences, Vol. 11, No. 5, pp. 397-400, 2004.

B. Ramasubramanian, “A New Wide Input-Range FGMOS Based Four Quadrant Multiplier with Electrical Error Correction,” Proceeding of the 2007 International Symposium on Circuits and Systems (ISSCS 07), pp. 1-4, 2007.

Y. Wang, Y. Wang, G. Tarr and K. Iniewski, “A Temperature, Supply Voltage Compensated Floating-Gate MOS Dosimeter Using VTH Extractor,” Proceeding of the 5th International Workshop on System-on-Chip for Real-Time Applications (IWSOC 05), pp 176-179, 2005.

Y. Wang, G. Tarr and Y. Wang, “A Novel Fully Integrated Floating-Gate MOSFET Radiation Dosimeter Using VTH Extractor,” Proceeding of the 2nd Annual IEEE Northeast Workshop on Circuits and Systems (NEWCAS 04), pp 9-12, 2004.

P. Mej´ıa-Ch´avez, J. C. Snchez-Garc´ıa, J. Vel´azquez-L´opez, “Differential Difference Amplifier FGMOS for Electrocardiogram Signal Acquisition,” Proceeding of the 2011 8th International Conference on Electrical Engineering Computing Science and Automatic Control (CCE 011), pp. 1-5, October 2011.

G. Kapur, S. Mittal, C. M. Markan and V.P. Pyara, “Analog Field Programmable CMOS Current Conveyor,” Proceeding of the 2012 Students Conference on Engineering and Systems (SCES 12), pp. 1-6, 2012.

F. Khateb, N. Khatib and D. Kub´anek, “Novel Ultra-Low-Power Class AB CCII+ Based on Floating-Gate Folded Cascode OTA,” Circuits Systems and Signal Processing, Vol. 31, No. 2, pp. 447-464, 2012.

K. Gupta, M. Bhardwaj, B.P. Singh and R. Choudhary, “Design of Low Power Low Cost True RMS-to-DC Converter,” Proceeding of the 2012 Second International Conference on Advanced Computing & Communication Technologies (ACCT 12), pp. 364-367, 2012.

R. Pandey and M. Gupta, “FGMOS Based Voltage-Controlled Grounded Resistor,” Radio Engineering, Vol. 19, No. 3, pp. 455-459, 2010.

M. Gupta and R. Pandey, “Low-Voltage FGMOS Based Analog Building Blocks,” Micro-electronics Journal, Vol. 42, No. 6, pp. 903-912,2011.

M. Gupta and R. Pandey, “FGMOS Based Voltage-Controlled Resistor and Its Applications,” Microelectronics Journal, Vol. 41, No. 1,pp. 25-32, 2010.

V Suresh Babu, P. S. Haseena and M. R. Baiju, “A Floating Gate MOSFET Based Current Reference with Subtraction Technique,” Proceeding of the 2010 IEEE Computer Society Annual Symposium on VLSI (ISVLSI 10), pp. 206-209, 2010.

S. Siskos, “FGMOSFET Based Built-In Current Sensor for Low Supply Voltage Analog and Mixed-Signal Circuits Testing,” Proceeding of the 2010 IEEE Computer Society Annual Symposium on VLSI (ISVLSI 10), pp. 259-264, 2010.

M-C J. Antonio, G-C Lizeth and G-C Felipe, “Floating-Gate MOSFET Parallel Analog Network for Assignment Problems,” Proceeding of the 2010 7th International Conference on Electrical Engineering Computing Science and Automatic Control (CCE 10), pp. 556-559, 2010.

J. M. A. Miguel, A. J. Lopez-Martin, L. Acosta, J. Ramrez-Angulo, and R. G. Carvajal, “Using Floating Gate and Quasi-Floating Gate Techniques for Rail-To-Rail Tunable CMOS Transconductor Design,” IEEE Transactions on Probabilistic Modelling of Variation in FGMOSFET Devices 61 Circuits and Systems I: Regular Papers, Vol. 58, No. 7, pp. 1604-1614, 2011.

A. J. Lopez-Martin, J. Ramrez-Angulo, R. G. Carvajal, and L. Acosta, “CMOS Transconductors with Continuous Tuning Using FGMOS Balanced Output Current Scaling,” IEEE Journal of Solid-State Circuits, Vol. 43, No. 5, pp. 1313-1323, 2008.

V. Srinivasan, G. Serrano, C. M. Twigg, and P. Hasler, “A Floating-Gate-Based Programmable CMOS Reference,” IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 55, No. 11, pp. 3448-3456, 2008.

Y. L. Wong, M. H. Cohen and P. A. Abshire, “A Floating-Gate Comparator with Automatic Offset Adaptation for 10-bit Data Conversion,” IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 52, No. 7, pp. 1316-1326, 2005.

Y. L. Wong, P. Xu, and P. Abshire, “Ultra-Low Spike Rate Silicon Neuron,” Proceeding of the 2007 IEEE Biomedical Circuits and Systems

Conference (BioCAS 07), pp. 95-98, November 2007.

K. Hasegawa, M. Aoki, T. Yamawaki, S. Tanaka, “Modelling Transistor Variation Using α-Power Formula and Its application to Sensitivity Analysis on Harmonic Distortion in Differential Amplifier,”

Analog Integrated Circuits and Signal Processing, Vol. 72, No. 3, pp. 605-613, 2011.

H. Masuda, T. Kida and S. Ohkawa, “Comprehensive Matching Characterization of Analog CMOS Circuits,” IEICE Transaction on Fundamental of Electronics, Communications and Computer Sciences, Vol. E92-A, No. 4, pp. 966-975, 2009.

S. Vlassis, S. Siskos, “Current-Mode Non-Linear Building Blocks Based on Floating-Gate Transistors,” Proceeding of the 2000 International Symposium on Circuits and Systems (ISCAS 00), pp.

-524, 2000.

C. Y. Kwok and H. R. Merhrvarz, “Low Voltage and Mismatch Analysis of Quadruple Source Coupled Multi-input Floating-Gate MOSFET Multiplier with Offset Trimming,” Analog Integrated Circuits and Signal Processing, Vol. 26,No. 2, pp. 141-156, 2001.

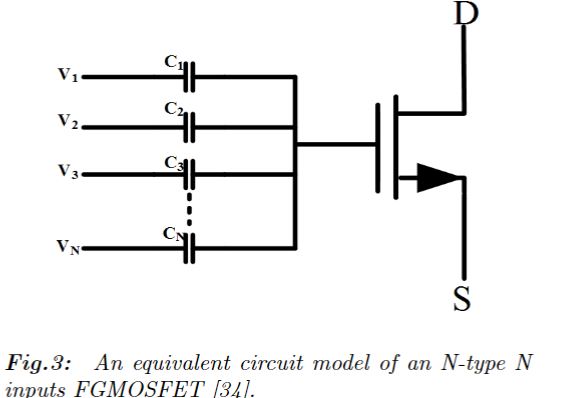

S. Vlassis and S. Siskos, “Design of Voltage-Mode and Current-Mode Computational Circuits Using Floating-Gate MOS Transistors,” IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 51, No. 2, pp. 329-341, 2004.

A. El mourabit, P. Pittet, G. N. Lu, “A widelinear range subthreshold OTA based on FGMOS transistor,” Proceedings of the 2004 11th IEEE International Conference on Electronics, Circuits and Systems (ICECS 04), pp. 17-20, 2004.

A. El mourabit, P. Pittet, G. N. Lu, “A low voltage highly linear CMOS OTA,” Proceedings. The16th International Conference on Microelectronics (ICM 04), pp. 700-703, 2004.

S. Vlassis and S. Siskos, “Differential-Voltage Attenuator Based on Floating-Gate MOS Transistors and Its Applications,” IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, Vol. 48, No. 11, pp. 1372-1378, 2001.

Y. Zhai and P. A. Abshire, “Adaptive Log Domain Filters for System Identification Using Floating Gate Transistors,” Analog Integrated Circuits and Signal Processing, Vol. 56, No. 1, pp. 23-36, 2008.

V. Suresh Babu, Salini Devi R., Ambika Sekhar and M. R. Baiju, “FGMOSFET Circuit for Neuron Activation Function and Its Derivative,” Proceeding of the 2009 4th IEEE Conference on Industrial Electronics and Applications (ICIEA 09), pp. 739-744, 2009.

J. Alfredsson and S. Aunet, “Trade-offs for high yield in 90 nm subthreshold floating-gate circuits by Monte-Carlo simulations,” Proceedings of IFIP VLSI-SOC Conference 2008 (VLSI-SOC 08), pp. 1-4, 2008.

R. Banchuin, “Analytical Model of Random Variation in Drain Current of FGMOSFET,” Active and Passive Electronic Components, Vol. 2015, pp. 1-12, 2015.

R. Banchuin and R. Chaisricharoen, “The probabilistic modeling of random variation in FGMOSFET,” Proceedings of the 2016 13th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON'16), pp. 1-5, 2016.

Y. Ye, S. Gummalla, C.-C.Wang, C. Chakrabarti and Y. Cao,“Random Variability Modeling and Its Impact on Scaled CMOS Circuits,” Journal of Computational Electronics, Vol. 9, No. 3, pp. 108-113, 2010.

S. Bhunia and S. Mukhopadhyay, Low Power Variation Tolerant and Design in Nanometer Silicon, Springer Science+Business Media, LLC,

New York, 2011, ch. 1.

K. Takeuchi, A. Nishida and T. Hiramoto, “Random Fluctuations in Scaled MOS Devices,” Proceeding of the 2009 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD 09), pp. 79-85, 2009.

T. Mogami, “Perspective of CMOS Technology and Future Requirement,” Proceedings of SPIE, the International Society for Optical Engineering, pp. 774802-1-774802-9, 2010.

J. Ramirez-Angulo, G. Gonzlrlez-Altamirano and S. C. Choi, “Modelling Multiple-Input Floating-Gate Transistors for Analog Signal Processing,” Proceeding of the 1997 International Symposium on Circuits and Systems (ISCAS97), pp. 2020-2023, 1997.

T. Altiok and B. Melamed, Simulation Modelling and Analysis with ARENA, Elsevier, Inc., United States, 2007, ch. 8.

S.A. Klugman, H.H Panjer and G.E. Willmot, Loss Models: From Data to Decisions, John Wiley and Sons, Inc., United States, 2008, ch. 13.

W.W. Hines, D.C. Montgomery, D.M. Goldsman and C.M. Borror, Probability and Statistics in Engineering, John Wiley and Sons, Inc., United States, 2003, ch. 3.

C. Forbes, M. Evans, N. Hastings and B. Peacock, Statistical Distributions, 4th ed., John Wiley and Sons, Inc., New York, 2011, ch. 2.

A.S. Medina-Vazquez, J. de la Cruz-Alejo, F. Gomez-Castaneda and J. A. Moreno-Cadenas, “Low-Voltage Linear Transconductor and A memory Current Using The MIFGMOS Transistor,” International Journal of Electronics, Vol. 96, No. 9, pp. 895-914, 2009.

G. Cijan, T. Tuma and A. Burmen, “Modelling and Simulation of MOS Transistor Mismatch,” Proceeding of the 6th Eurosim Congress on Modeling and Simulation (EUROSIM 07), pp. 1-8, 2007.