Model-Based Design Optimization using CDFG for Image Processing on FPGA

Main Article Content

Abstract

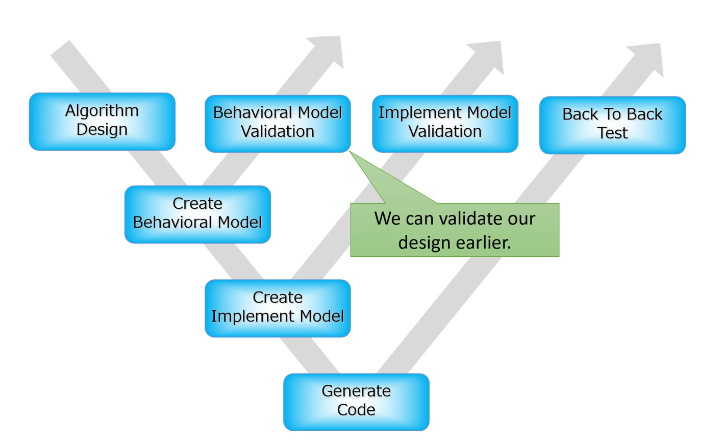

As the automotive industry moves toward autonomous driving and ADAS (Advanced Driver Assistance Systems), Model-Based Design (MBD) is a practical design methodology. It can be used to develop rapid prototyping by using MATLAB and Simulink. The MBD method still has limitations for handling complex models. This paper uses the Control Data Flow Graph (CDFG), an intermediate representation for analyzing complex algorithms, so that suitable optimizations for image processing applications can be implemented on an FPGA. The experimental results show that the proposed CDFG method improved both the area and speed of the edge detection case study compared with the MathWorks Vision HDL toolbox.

Article Details

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

References

J.C. Ting Hai, O. Chee Pun, and T. Wooi Haw, “Accelerating Video and Image Processing Design for FPGA using HDL Coder and Simulink,” in 2015 IEEE Conference on Sustainable Utilization and Development in Engineering and Technology (CSUDET), pp. 28-32, 2015.

S. Titri, C. Larbes and K. Y. Toumi, “Rapid prototyping of PVS into FPGA: From Model-Based Design to FPGA/ASICs Implementation,” 2014 9th International Design and Test Symposium (IDT), Algeries, Algeria, pp. 162-167, 2014.

N. Othman, M. H. Jabbar, A. K. Mahamad and F. Mahmud, “Luo Rudy Phase I Excitation Modeling towards HDL Coder Implementation for Real-time Simulation,” 2014 5th International Conference on Intelligent and Advanced Systems (ICIAS), Kuala Lumpur, Malaysia, pp. 1-6, 2014.

N. Othman, F. Mahmud, A. Kadir Mahamad, M. Hairol Jabbar and N. Atiqah Adon, “Cardiac Excitation Modeling: HDL Coder Optimization towards FPGA Stand-alone Implementation,” in 2014 IEEE International Conference on Control System, Computing and Engineering, pp. 507-512, 2014.

M. Besbes, S. H. Sa ̈ıd and F. M’Sahli, “FPGA Implementation of High Gain Observer for Induction Machine Using Simulink HDL Coder,” 2015 3rd International Conference on Control, Engineering & Information Technology (CEIT), Tlemcen, Algeria, pp. 1-6, 2015.

S. Cheng, and J. Wawrzynek, “High-Level Synthesis with a Dataflow Architectural Template,” in 2nd International Workshop on Overlay Architectures for FPGAs (OLAF2016), pp. 288-293, 2016.

MathWorks, “Limitations for MATLAB Loop Optimization,” HDL coder user guide, pp. 8-30, 2023.

Advanced Micro Devices, Vitis High-Level Synthesis User Guide (UG1399), https://docs. xilinx.com/r/en-US/ug1399-vitis-hls/ Creating-Additional-Solutions, 2023.

Xilinx, Improving Performance, 2016.

E. Kim, J. Lee, and D. Lee, “Automatic ProcessOriented Asynchronous Control Unit Generation from Control Data Flow Graphs,” IEICE Trans. on Fundamentals, vol. E84-A, no. 8, pp. 2014-2028, August 2001.

G. De Micheli, Synthesis and Optimization of Digital Circuits, McGraw-Hill, 1994.

The MathWorks, Inc., Vision HDL ToolboxTM Reference, 2023.