Streaming Accelerator Design for Regular Expression on CPU+FPGA Embedded System

Main Article Content

Abstract

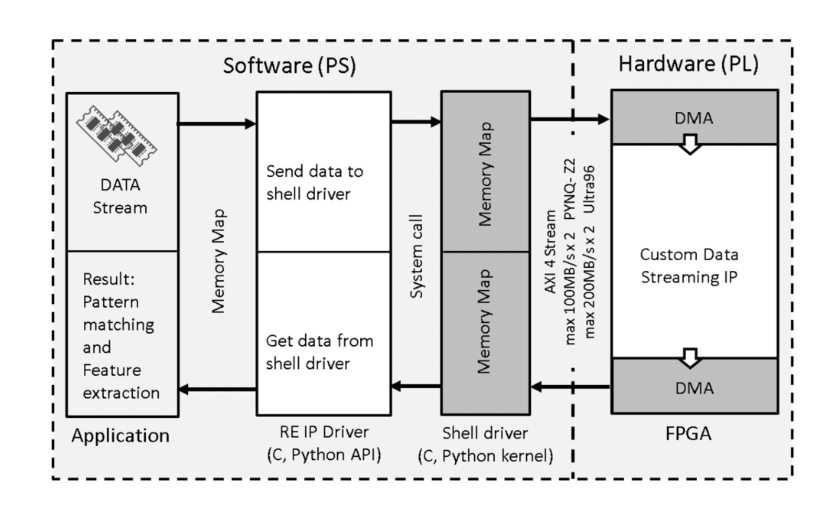

A pattern matching application is one of the necessary tasks in streaming data processing. A hardware accelerator employing FPGA can be faster than a general-purpose processor in performing data pattern matching using regular expression methods. However, it is difficult and time-consuming to design the hardware on the FPGA for each regular expression pattern. We are researching a method for automatically designing hardware accelerators for higher efficiency and performance to improve user productivity. In this research, we propose rules and methods for translating regular expression patterns into supported hardware code as our contribution to providing an efficient design method for regular expression hardware accelerators and allowing the efficient utilization of FPGAs. The performance evaluation is compared with the regular expression algorithm on ARM processors, CPU servers, and FPGA data streaming applications. Our result shows that our FPGA accelerator enables speeding up data streaming applications on CPU processors. Our solution is 733 times faster than optimized C/C++ code. It is 70 times faster than using the Python library. It is twice as fast as PYNQ-Z2 and 1.5 faster than RE2C. Furthermore, our proposed accelerator Ultra-96 improves the performance 2 times with an 8[MB/J] high energy efficiency from the previous PYNQ-Z2 approach.

Article Details

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

References

K. Yasumoto, H. Yamaguchi and H. Shigeno, “Survey of Real-time Processing Technologies of IoT Data Streams,” Journal of Information Pro- cessing, vol. 24, no. 2, pp. 195-202, 2016.

K.S. Bok, D. Kim and J. Yoo, “Complex Event Processing for Sensor Stream Data,” Sensors, vol. 18, no.9, 2018.

W. McKinney, Python for Data Analysis: Data Wrangling with Pandas, NumPy, and IPython, O’reilly, 2017.

J. Teubner and L. Woods, Data Processing on FPGAs, Springer, 2013.

Vivado Design Suite User Guide High-Level Syn- thesis UG902. (2019). UG902 (v2020.1) June 3, 2020.

K. Carruthers, “How the internet of things changes everything: The next stage of the digital revolution,” Journal of Telecommunications and the Digital Economy, vol. 2, no.4, 2014.

R.P. Sidhu and V. Prasanna, “Fast Regular Expression Matching Using FPGAs,” The 9th IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM’01), pp. 227- 238, 2001.

L. Woods, J. Teubner and G. Alonso, “Complex event detection at wire speed with FPGAs,” Proceedings of the VLDB Endowment, vol .3, pp. 660-669, 2010.

V. Paxson, S. Campbell, C. Leres and J. Lee, Bro Intrusion Detection System, 2006.

S. Prithi, S. Sumathi and C. Amuthavalli, A Survey on Intrusion Detection System using Deep Packet Inspection for Regular Expression Match- ing, 2017.

S.A. Shah and B. Issac, “Performance Comparison of Intrusion Detection Systems and Application of Machine Learning to Snort System,” Future Gener. Comput. Syst., vol. 80, pp. 157- 170, 2018.

L. Woods, J. Teubner and G. Alonso, “Real-time pattern matching with FPGAs,” 2011 IEEE 27th International Conference on Data Engineering, pp. 1292-1295, 2011.

Y. Yang and V. Prasanna, “High-Performance and Compact Architecture for Regular Expression Matching on FPGA,” IEEE Transactions on Computers, vol. 61, pp. 1013-1025, 2012.

W.P. Kiat, K.M. Mok, W. Lee, H.G. Goh and R. Achar, “An energy efficient FPGA partial reconfiguration based micro-architectural technique for IoT applications,” Microprocess and Microsystems, vol.73, 2020.

J. Cong, B. Liu, S. Neuendorffer, J. Noguera, K. Vissers and Z. Zhang, “High-Level Synthesis for FPGAs: From Prototyping to Deployment,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol .30, pp. 473-491, 2011.

P. Bumbulis and D. Cowan, “RE2C: a more versatile scanner generator,” ACM Letters on Programming Languages and Systems, vol. 2, pp. 70- 84, 1993.

U. Trofimovich, “RE2C: A lexer generator based on lookahead-TDFA,” Software Impacts, vol. 6, 2020.

https://data.world/brianray/enron-email-dataset

Hendarmawan, M. Kuga and M. Iida, “Translation Rules of Regular Expression Code for Hardware Accelerator,” Proc. of Asia pacific Conference on Robot IoT System Development and Platform, Digital Library, Information Processing Society of Japan, pp. 51-58, March 15th, 2021.

Vivado design suite user guide: Highlevel synthesis, UG902 (v2019.1) August 12, 2021. [Online]. Available: https://www.xilinx.com/support/ documentation/sw_manuals/xilinx2019_ 1/ug902-vivado-high-level-synthesis.pdf