Two-Dimensional Error Correction Code for Spin-Transfer Torque Magnetic Random-Access Memory (STT-MRAM) Caches

Main Article Content

Abstract

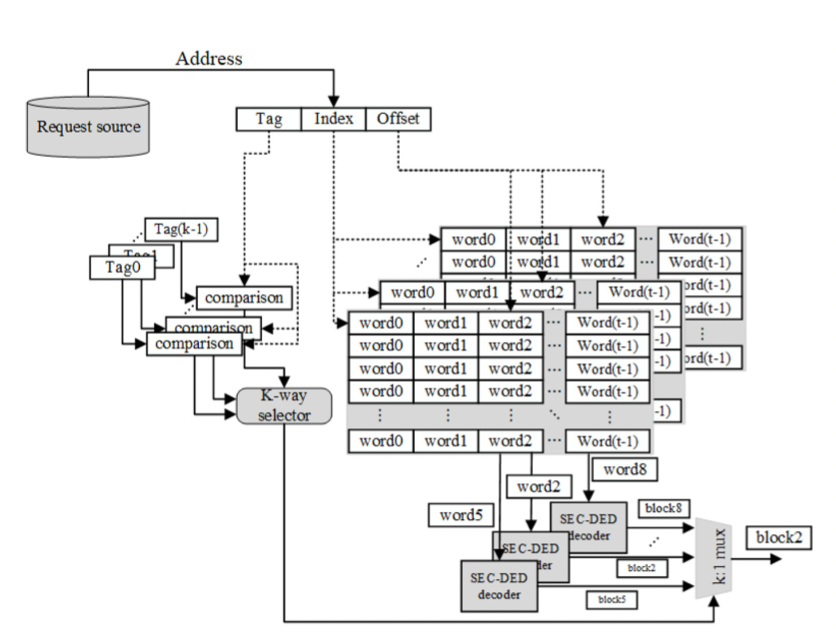

Spin-Transfer Torque Magnetic Random-Access Memory (STT-MRAM) is an emerging nonvolatile memory (NVM) technology that can replace conventional cache memory in computer systems. STT-RAM has many desirable properties such as high writing and reading speed, non-volatility, and low power consumption. Since the cache requires a high speed of writing and reading speed, a single-error correction and double error detection (SEC - DED) are applicable to improve the reliability of the cache. However, the process variation and thermal fluctuation of STT-MRAM cause errors. For example, writing ‘1’ bits has more errors than writing ‘0’ bits. We then design the weight reduction code to reduce the error caused by writing ‘1’ bits. Moreover, the performance of an SEC-DED code is improved by constructing an SED-DED code as the product code. The simulation results demonstrate that the two-dimensional error correction code consisting of product code and weight reduction code is roughly 5.67 × 10−4 lower than the SEC-DED code when the error rate of writing ‘1’ bits is equal to 6 × 10−3.

Article Details

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

References

H. Jingtong, C. J. Xue, Q. Zhuge, W. Tseng, and E. Sha, “Towards energy efficient hybrid on-chip scratch pad memory with non-volatile memory,” {it in Proc. IEEE 14th Int. Conf. DATE, Grenoble, France}, Mar. 14–18, 2011, pp. 1–6.

H. Noguchi et al., “7.2 4mb stt-mram-based cache with memory-accessaware power optimization and write-verify-write / read-modify-write scheme,” {it in 2016 IEEE International Solid-State Circuits Conference (ISSCC)}, Jan 2016, pp. 132–133.

W. Xu, H. Sun, Y. Chen, and T. Zhang. “Design of Last-Level On-Chip Cache Using Spin-Torque Transfer RAM (STT-RAM),” {it in IEEE Trans. on VLSI System}, pages 483–493. IEEE, 2011.

P. Zhou, B. Zhao, J. Yang, and Y. Zhang. “Energy Reduction for STTRAM Using Early Write Termination,” {it in ICCAD}, pages 264–268. ACM, 2009.

M. Hsiao. “A Class of Optimal Minimum Odd-weight-column SEC-DED Codes,” {it IBM Journal of Research and Development}, 14(4):395–401, 1970.

J. Yang, B. Geller, M. Li, and T. Zhang, “An information theory perspective for the binary STT-MRAM cell operation channel,” {it IEEE Trans. Very Large Scale Integr. (VLSI) Syst.}, vol. 23, no. 4, pp. 979 - 991, Mar. 2016.

C. W. Smullen, IV, A. Nigam, S. Gurumurthi, and M. R. Stan, “The stetsims stt-ram simulation and modeling system,” {it in ICCAD}, 2011.

L. Zhang et al., “Channel Modeling and Reliability Enhancement Design Techniques for STT-MRAM," 2015 IEEE Computer Society Annual Symposium on VLSI, 2015, pp. 461-466, doi: 10.1109/ISVLSI.2015.125.

B. Li, Y. Pei and W. Wen, “Efficient Low-Density Parity-Check (LDPC) Code Decoding for Combating Asymmetric Errors in STT-RAM," 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2016, pp. 266-271, doi: 10.1109/ISVLSI.2016.9.

X. Zhong, K. Cai, Z. Mei and T. Q. S. Quek, “Deep Learning-Based Decoding of Linear Block Codes for Spin-Torque Transfer Magnetic Random Access Memory," in IEEE Transactions on Magnetics, vol. 57, no. 2, pp. 1-5, Feb. 2021, Art no. 3400605, doi: 10.1109/TMAG.2020.3021405.

J. Yang, B. Geller, M. Li, and T. Zhang, “An information theory perspective for the binary STT-MRAM cell operation channel,” {it IEEE Trans. Very Large Scale Integr. (VLSI) Syst.}, vol. 23, no. 4, pp. 979 - 991, Mar. 2016.

H. Farbeh, H. Kim, S. G. Miremadi and S. Kim, “Floating-ECC: Dynamic Repositioning of Error Correcting Code Bits for Extending the Lifetime of STT-RAM Caches," in IEEE Transactions on Computers, vol. 65, no. 12, pp. 3661-3675, 1 Dec. 2016, doi: 10.1109/TC.2016.2557326.

Z. Azad, H. Farbeh and A. M. H. Monazzah, “ORIENT: Organized interleaved ECCs for new STT-MRAM caches," 2018 Design, Automation $&$ Test in Europe Conference $&$ Exhibition (DATE), 2018, pp. 1187-1190, doi: 10.23919/DATE.2018.8342194.

A. Ahari, M. Ebrahimi, F. Oboril and M. Tahoori, “Improving reliability, performance, and energy efficiency of STT-MRAM with dynamic write latency," 2015 33rd IEEE International Conference on Computer Design (ICCD), 2015, pp. 109-116, doi: 10.1109/ICCD.2015.7357091.

E. Aliagha, A. M. H. Monazzah and H. Farbeh, “REACT: Read/Write Error Rate Aware Coding Technique for Emerging STT-MRAM Caches," in IEEE Transactions on Magnetics, vol. 55, no. 5, pp. 1-8, May 2019, Art no. 3400808, doi: 10.1109/TMAG.2019.2905523.

R. Bishnoi, M. Ebrahimi, F. Oboril and M. B. Tahoori, “Improving Write Performance for STT-MRAM," in IEEE Transactions on Magnetics, vol. 52, no. 8, pp. 1-11, Aug. 2016, Art no. 3401611, doi: 10.1109/TMAG.2016.2541629.

S.-S. Pyo, C.-H. Lee, G.-H. Kim, K.-M. Choi, Y.-H. Jun, and B.-S. Kong, “45nm low-power embedded pseudo-SRAM with ECC-based auto-adjusted self-refresh scheme,” in 2009 IEEE International Symposium on Circuits and Systems (IEEE, 2009), p. 2517.

P. Reviriego, A. Sanchez-Macian, and J. A. Maestro, “Low power embedded DRAM caches using BCH code partitioning,” in 2012 IEEE 18th International On-Line Testing Symposium (IOLTS) (IEEE, 2012), p. 79.

Y. Li, H. Zhong, R. Danilak, and E. T. Cohen, (Google Patents, 2014).

B. Del Bel, J. Kim, C. H. Kim, and S. S. Sapatnekar, “Improving STT-MRAM density through multibit error correction,” in Design, Automation and Test in Europe Conference and Exhibition (DATE), 2014 (IEEE, 2014), p. 1.

X. Guo, M. N. Bojnordi, Q. Guo, and E. Ipek, “Sanitizer: Mitigating the impact of expensive ECC checks on STT-MRAM based main memories,” IEEE Trans. Comput. 67, 847 (2017).

C. Yang, Y. Emre, Y. Cao, and C. Chakrabarti, “Improving reliability of non-volatile memory technologies through circuit level techniques and error control coding,” EURASIP J. Adv. Signal Process. 2012, 211.

X. Zhong, K. Cai, P. Chen and Z. Mei, “Rate-Compatible Protograph LDPC Codes for Spin-Torque Transfer Magnetic Random Access Memory (STT-MRAM)," 2018 Asia-Pacific Magnetic Recording Conference (APMRC), 2018, pp. 1-2, doi: 10.1109/APMRC.2018.8601078.

W. Wen, M. Mao, X. Zhu, S. H. Kang, D. Wang, and Y. Chen, “CD-ECC: Content-dependent error correction codes for combating asymmetric nonvolatile memory operation errors,” {it in Proc. IEEE/ACM Int. Conf. Comput.-Aided Design (ICCAD)}, Nov. 2013, pp. 1–8.

E. Cheshmikhani, H. Farbeh and H. Asadi, “Enhancing Reliability of STT-MRAM Caches by Eliminating Read Disturbance Accumulation," {it in 2019 Design, Automation & Test in Europe Conference & Exhibition (DATE)}, Mar. 2019.

C. L. Chen and M. Y. Hsiao, “Error-Correcting Codes for Semiconductor Memory Applications: A State-of-the-Art Review," in IBM Journal of Research and Development, vol. 28, no. 2, pp. 124-134, March 1984, doi: 10.1147/rd.282.0124.

S. Lin and D. J. Costello, Error Control Coding, 2nd ed. Upper Saddle River, NJ: Pearson Education.

J. Kim et al., “Multi-bit error tolerant caches using two-dimensional error coding,” in Proc. 40th IEEE/ACM Int. Symp. Microarch., 2008, pp. 197–209.

B. Fu and P. Ampadu, “Burst error detection hybrid ARQ with crosstalk-dealy reduction for reliable on-chip interconnects,” in Proc. 24th IEEE Int. Symp. Defect Fault Toler. VLSI Syst., 2009, pp. 440–448