Scalable Hardware Mechanism for Partitioned Circuits Operation

Main Article Content

Abstract

For designing hardware with a high-level synthesis tool using a programming language such as C or Java, its large size of logic circuit makes it difficult to implement the design in a single FPGA. In such a case, partitioning the logic circuit and implementing in multiple FPGAs is a commonly used approach.

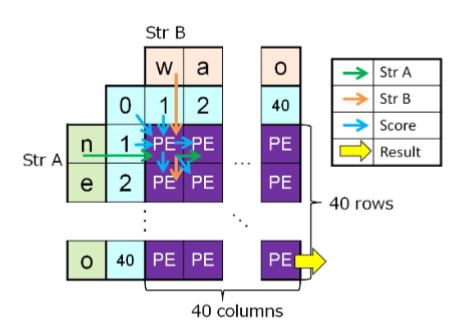

We propose the Scalable Hardware Mechanism, which enables the operation of a partitioned circuit to prevent the degradation of clock frequency by minimizing its dependence on the usage and the type of FPGA. Our mechanism provides a reduced delay by the collective signal transmission with the partitioned AES code generation circuit and the character string edit distance calculation circuit as partitioned circuits. The collective signal transmission has attained 1.27 times improvement in the speed for the AES code generation circuit and 3.16 times improvement for the character string edit distance calculation circuit compared with the circuit by the conventional method.

Article Details

References

[2] O. Mencer, K. H. Tsoi, S. Craimer, T. Todman, W. Luk, M. Y. Wong, and P. H. W. Leong, "Cube: A 512-fpga cluster In Programmable Logic," 2009 5th Southern Conference on Programmable Logic (SPL), Sao Carlos, pp.51-57,2009.

[3] K.Takahashi, R.Saeki, M.Kuga and T.Sueyoshi, "Circuit Partitioning Techniques for FPGA-based ASIC Emulator via High-speed Serial Communication," Proc. 2011 Joint Conference of Electrical and Electronics Engineers in Kyusyu, 11-1P-03, pp.249-250, 2011.

[4] K.Takahashi, M.Amagasaki, M.Kuga, M.Iida, T.Sueyoshi, "Circuit Partitioning Methods for FPGA-based ASIC Emulator using High-speed Serial Wires," Proc. The 17th Workshop on Synthesis And System Integration of Mixed Information Technologies(SASIMI2012), pp.317-318, 2012.

[5] M. Turki, Z. Marrakchi, H. Mehrez and M. Abid, "Frequency Optimization Objective during System Prototyping on Multi-FPGA Platform," International Journal of Recon gurable Computing, Volume 2013, Article ID 853510, 2013.

[6] Shinya Takamaeda-Yamazaki: Pyverilog: "A Python-based Hardware Design Processing Toolkit for Verilog HDL,"

11th International Symposium on Applied Recon gurable Computing (ARC 2015) (Poster), Lecture Notes in Computer Science, Vol.9040/2015, pp.451-460, 2015.