# Robust Digital Control for Interleaved PFC Boost Converter Using Approximate 2DOF

**Yuki Satake<sup>1</sup>, Hiroyuki Furuya<sup>2</sup>, Yohei Mochizuki<sup>3</sup>, Yuji Fukaishi<sup>4</sup>,

Kohji Higuchi<sup>5</sup>, Non-members, and Kosin Chamnongthai<sup>6</sup>, Member**

## ABSTRACT

In recent years, improving of power factor and reducing harmonic distortion in electrical instruments are needed. In general, a current conduction mode boost converter is used for active PFC (Power Factor Correction). In a PFC boost converter, if a duty ratio, a load resistance and an input voltage are changed, the dynamic characteristics are varied greatly. This is the prime reason of difficulty of controlling the interleaved PFC boost converter. In this paper, a robust digital controller for suppressing the change of step response characteristics and variation of output voltage at a DC-DC buck converter load sudden change with high power factor and low harmonic is proposed. Experimental studies using a micro-processor for controller demonstrate that the proposed digital controller is effective to improve power factor and to suppress output voltage variation.

**Keywords:** Power Factor Correction (PFC), Boost Converter, Approximate 2DOF, Digital Robust Control, Micro-processor

## 1. INTRODUCTION

In recent years, improving of power factor and reducing harmonic of power supply using nonlinear electrical instruments are needed. A passive filter and an active filter in AC lines are used for improving of the power factor and reducing the harmonic [1-2]. Generally a current conduction mode boost converter is used for an active PFC (Power Factor Correction) in electrical instruments. Especially, an interleave PFC boost converter is used in order to make a size compact, make an efficiency high and

make noise low. In the interleave PFC boost converter, if a duty ratio, a load resistance and an input voltage are changed, the dynamic characteristics are varied greatly, that is, the interleave PFC converter has nonlinear characteristics. In many applications of the interleave PFC converters, loads cannot be specified in advance, i.e., their amplitudes are suddenly changed from the zero to the maximum rating. This is the prime reason of difficulty of controlling the interleave PFC boost converter.

Usually, a conventional PI, an analog IC controller, a gainscheduled controller designed to the approximated linear controlled object at one operating point is used for the PFC converter [3-6]. In the nonlinear interleaved PFC boost converter system, those controller are not enough for attaining good performance [7-9]. In this paper, the robust controller for suppressing the change of step response characteristics and variation of output voltage at a DC-DC buck converter load sudden change with high power factor and low harmonic is proposed. An approximate 2-degree-of-freedom (A2DOF) method [10-11] is applied to the interleave PFC boost converter with a DC-DC buck converter load. The PFC converter is a nonlinear system and the models are changed at each operation point. The design and combining methods of two A2DOF controllers which can cope with nonlinear system or changing of the models with one controller is proposed. The DC-DC buck converter load is also controlled using A2DOF [10]. These three controllers are actually implemented on one micro processor and is connected to the PFC converter and the load. Experimental studies demonstrate that the digital controllers designed by the proposed method is effective to improve power factor and to suppress output voltage variation.

## 2. INTERLEAVED PFC BOOST CONVERTER WITH DC-DC CONVERTER LOAD

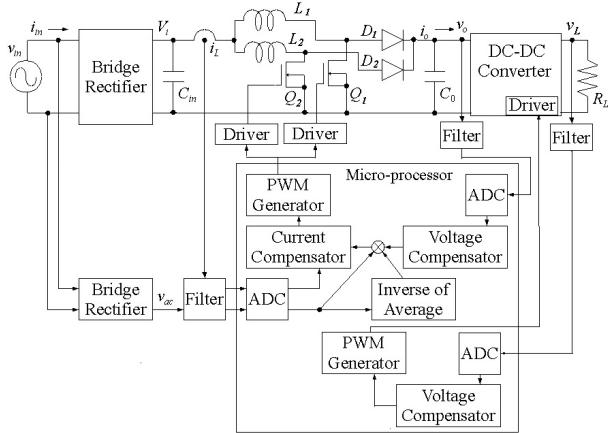

The interleaved PFC boost converter with DC-DC converter load shown in Fig. 1 is manufactured.

In Fig.1,  $v_{in}$  is an input AC voltage,  $v_{ac}$  is an absolute value of the input AC voltage,  $i_{in}$  is an input AC current,  $C_{in}$  is a smoothing capacitor,  $V_i$  is a rectifying and smoothing input voltage, and  $v_o$  is an output voltage of PFC.  $Q_1$  and  $Q_2$  are MOSFETs or IGBTs,  $L_1$  and  $L_2$  are interleave boost inductances,  $D_1$  and  $D_2$  are interleave

Manuscript received on July 6, 2013 ; revised on November 18, 2013.

Final manuscript received April 20, 2014.

<sup>1,2,4</sup> The authors are with SANSHIN ELECTRIC CO., LTD. 4-1-5, Koyama Nerima-ku, Tokyo 176-0022, Japan, E-mail: ysatake@sanshin-ele.co.jp, hfuruya@sanshin-ele.co.jp and yfukaishi@sanshin-ele.co.jp

<sup>3,5</sup> The authors are with The University of Electro-Communications 1-5-1, Chofu-ga-oka, Chofu-shi, Tokyo 182-8585, Japan, E-mail: mochduki@francis.ee.uec.ac.jp and higuchi@ee.uec.ac.jp

<sup>6</sup> The author is with KMUTT, 126 Pracha-uthit Rd., Bangmod, Tungkru, Bangkok 10140, Thailand, E-mail: kosin.cha@kmutt.ac.th

**Fig.1:** Interleaved PFC boost converter with DC-DC converter load.

boost diodes and  $i_L$  is the sum of inductor current,  $C_0$  is an output capacitor. DC-DC converter is a load of the PFC boost converter,  $R_L$  is an output load resistance of the DC-DC converter. Here  $V_{in}=100[V_{AC}]$ ,  $V_i=140[V_{DC}]$ ,  $v_o = 385[V_{DC}]$ ,  $L_1=L_2=350[\mu H]$ ,  $v_L=26[V_{DC}]$ ,  $N1:N2=10:1$ ,  $C_0=940[\mu F]$ , the switching frequency  $f_{sw}=50[kHz]$ , the sampling frequency  $f_s=100[kHz]$ .

The inductor current  $i_L$  is controlled to follow the rectified input voltage  $v_{ac}$  for improved power factor, reduced harmonic and stable the output voltage. Using the state-space averaging method, the state equation of the interleaved boost converter becomes as follows [12]:

$$\frac{d}{dt} \begin{bmatrix} i_L \\ v_o \end{bmatrix} = \begin{bmatrix} -\frac{R_0}{L_0} & -\frac{1}{L_0} \\ \frac{1}{C_0} & -\frac{1}{R_{LDC}C_0} \end{bmatrix} \begin{bmatrix} i_L \\ v_o \end{bmatrix} + \begin{bmatrix} \frac{V_i}{L_0} \\ 0 \end{bmatrix} (1) \\ + \left\{ v_o \begin{bmatrix} \frac{1}{L_0} \\ 0 \end{bmatrix} + i_L \begin{bmatrix} 0 \\ -\frac{1}{C_0} \end{bmatrix} \right\} \mu$$

Here  $\mu$  is duty ratio and  $R_{LDC}$  is DC-DC converter load to PFC boost converter. When controlling the current of the sum of each phase,  $R_0$  is  $R_1R_2/(R_1 + R_2)$  and  $L_0$  is  $L_1L_2/(L_1 + L_2)$ . The boost converter has non-linear characteristics because this equation has the product of state variable  $v_o$ ,  $i_L$  and duty ratio  $\mu$ .

#### A. Static characteristics of boost converter

At some operating point of eq. (1), let  $v_o$ ,  $i_L$  and  $\mu$ , be  $V_s$ ,  $I_s$  and  $\mu_s$ , respectively. Then the average of output voltage  $V_s$  and inductor current  $I_s$  at the operating points becomes as follows:

$$V_s = \frac{1}{1 + \frac{1}{(1 - \mu_s)^2} R_L} \frac{1}{1 - \mu_s} V_i \quad (2) \\ I_s = \frac{1}{R_L} \frac{V_s}{1 - \mu_s}$$

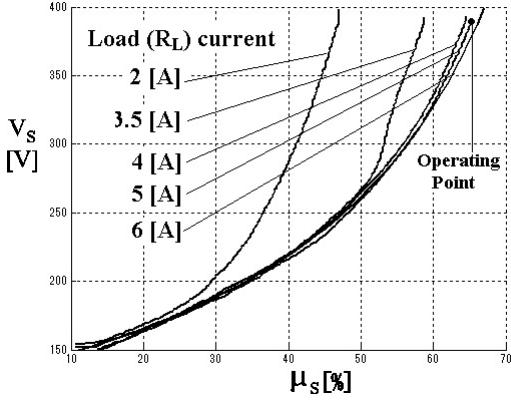

The actual measurement results of the static characteristics of  $\mu_s$  to  $V_s$  are shown in Fig.2. In Fig.2, it turns out that the boost converter is a non-linear system. The static characteristic of the boost converter is changed greatly with load resistances, and it influences the dynamic characteristics of converter. In addition, the static characteristics will be changed with input voltage variation.

#### B. Dynamic characteristics of boost converter

The linear approximate state equation of the boost converter using small perturbations  $\Delta i_L = i_L - I_s$ ,  $\Delta v_o = v_o - V_s$  and  $\Delta \mu = \mu - \mu_s$  is as follows:

$$\dot{x}(t) = A_c x(t) + B_c u(t) \\ y(t) = C_c x(t) \quad (3)$$

where

$$A_c = \begin{bmatrix} -\frac{R_0}{L_0} & -\frac{1 - \mu_s}{L_0} \\ \frac{1 - \mu_s}{C_0} & -\frac{1}{R_{LDC}C_0} \end{bmatrix}, \quad B_c = \begin{bmatrix} \frac{V_s}{L_0} \\ -\frac{I_s}{C_0} \end{bmatrix}$$

$$x(t) = \begin{bmatrix} \Delta i_L(t) \\ \Delta v_o(t) \end{bmatrix}, \quad u(t) = \Delta \mu(t), \quad y = \begin{bmatrix} y_i \\ y_v \end{bmatrix}, \quad C_c = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$$

From this equation, matrix  $A_c$  and  $B_c$  of the boost converter depends on duty ratio  $\mu_s$ . Therefore, the converter response will be changed depending on the operating point and other parameter variations. The changes of the load  $R_{LDC}$ , the duty ratio  $\mu_s$ , the output voltage  $V_s$  and the inductor current  $I_s$  in the controlled object are considered as parameter changes in eq. (3). Such parameter changes can be replaced with the equivalent disturbances inputted to the input and the output of the controlled object. Therefore, what is necessary is just to constitute the control systems whose pulse transfer functions from equivalent disturbances to the output  $y$  become as small as possible in their amplitudes, in order to robustize or suppress the influence of these parameter changes.

### 3. DIJITAL ROBUST CURRENT CONTROLLER

#### A. Discretization of controlled object

The continuous system of eq. (3) is transformed into the discrete system as follows:

**Fig.2:** The static characteristics of  $\mu_s$  to  $V_s$ .

$$\begin{aligned} x(k+1) &= A_d x(k) + B_d u(k) \\ y(k) &= C_d x(k) \end{aligned} \quad (4)$$

where

$$A_d = [e^{A_c T}] , B_d = \left[ \int_0^T e^{A_c \tau} B_c d\tau \right] , C_d = C_c$$

Here, in order to compensate the delay time by A/D conversion time and micro-processor operation time etc., one delay (state  $\xi_1$ ) is introduced to input of the controlled object. Then the state-space equation is described as follows:

$$\begin{aligned} x_{dt}(k+1) &= A_{dt} x_{dt}(k) + B_{dt} v(k) \\ y(k) &= C_{dt} x_{dt}(k) \end{aligned} \quad (5)$$

where

$$A_{dt} = \begin{bmatrix} e^{A_c T_s} & e^{A_c (T_s - L_d)} \int_0^{L_d} e^{A_c \tau} B_c d\tau \\ 0 & 0 \end{bmatrix} = \begin{bmatrix} a_{11} & a_{12} & a_{13} \\ a_{21} & a_{22} & a_{23} \\ 0 & 0 & 0 \end{bmatrix}$$

$$B_{dt} = \begin{bmatrix} \int_0^{T_s - L_d} e^{A_c \tau} B_c d\tau \\ 1 \end{bmatrix} = \begin{bmatrix} b_{11} \\ b_{21} \\ 1 \end{bmatrix} \quad x_{dt}(k) = \begin{bmatrix} x(k) \\ \xi_1(k) \end{bmatrix}$$

$$C_{dt} = [C_c \ 0] = [1 \ 0 \ 0]$$

#### B. Design method for A2DOF digital current controller

The transfer function from the reference input  $r'_i$  to the output  $y_i$  is specified as follows:

$$\begin{aligned} W_{r'_i y_i}(z) &= \frac{(1 + H_1)(1 + H_2)(1 + H_3)}{(z + H_1)(z + H_2)(z + H_3)} \\ &\times \frac{z - n_{1i}}{(1 - n_{1i})} \frac{(z - n_{2i})}{1 - n_{2i}} \end{aligned} \quad (6)$$

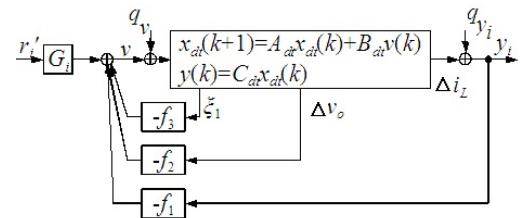

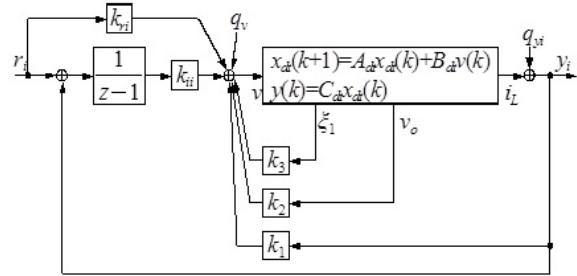

Here  $H_i$ ,  $i = 1, \dots, 3$  are the specified arbitrary parameters,  $n_{1i}$  and  $n_{2i}$  are the zeros of the discrete-time controlled object. This target characteristic  $W_{r'_i y_i}$  is realizable by constituting the model matching system shown in Fig. 3 using the following state feedback to the controlled object (5).

$$v = -F x_{dt} - G_i r'_i \quad (7)$$

Here  $F = [f_1 f_2 f_3]$  and  $G_i$  are selected suitably. In Fig. 3  $q_v$  and  $q_{y_i}$  are the equivalent disturbances with which the parameter changes of the controlled object are replaced.

**Fig.3:** Model matching system using state feedback.

It shall be specified that the relation of  $H_1$  and  $H_3$  become  $|H_1| \gg |H_3|$  and  $n_{1i} \approx H_2$ . Then  $W_{r'_i y_i}$  can be approximated to the following first-order discrete-time model:

$$W_{r'_i y_i}(z) \approx W_{mi}(z) = \frac{1 + H_1}{z + H_1} \quad (8)$$

The transfer function  $W_{Qy_i}(z)$  between the equivalent disturbance  $Q_i = [q_v \ q_{y_i}]^T$  to  $y_i$  of the system in Fig. 3 is defined as

$$W_{Qy_i}(z) = [W_{Qv y_i}(z) \ W_{Qy y_i}(z)] \quad (9)$$

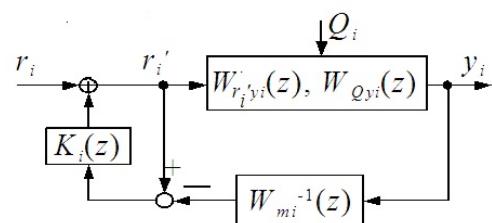

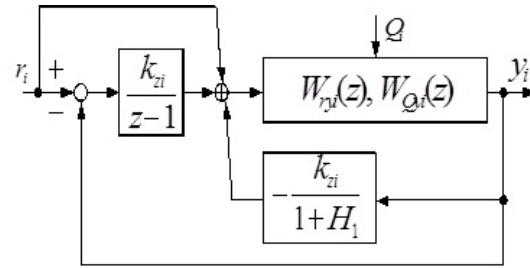

**Fig.4:** System reconstituted with inverse system and filter.

The system added the inverse system and the filter to the system of Fig. 3 is constituted as shown in Fig. 4.

In Fig. 4, the transfer function  $K_i(z)$  is as follows:

$$K_i(z) = \frac{k_{zi}}{z - 1 + k_{zi}} \quad (10)$$

The transfer functions between  $r_i - y_i$ ,  $q_v - y_i$  and  $q_{yi} - y_i$  of the system in Fig. 4 are given by

$$y_i = \frac{1 - H_1}{z + H_1} \frac{z - 1 + k_{zi}}{z - 1 + k_{zi} W_{si}(z)} W_{si}(z) r_i \quad (11)$$

$$y_i = \frac{z - 1 + k_{zi}}{z - 1 + k_{zi}} \frac{z - 1 + k_{zi}}{z - 1 + k_{zi} W_{si}(z)} W_{Qyi}(z) Q_i \quad (12)$$

where

$$W_{si}(z) = \frac{(1 + H_3)}{(z + H_3)} \frac{z - n_{1i}}{1 - n_{1i}}$$

Here, if  $W_{si}(z) \approx 1$ , then eq. (11) and eq. (12) are approximated, respectively as follows:

$$y_i \approx \frac{1 + H_1}{z + H_1} r_i \quad (13)$$

$$y_i \approx \frac{z - 1}{z - 1 + k_{zi}} W_{Qyi}(z) Q_i \quad (14)$$

From eq. (13), (14), it turns out that the characteristics from  $r$  to  $y$  can be specified with  $H_1$  and the characteristics from  $Q_i$  to  $y_i$  can be independently specified with  $k_{zi}$ . That is, the system in Fig. 4 is an A2DOF system, and its sensitivity against disturbances becomes lower with the increase of  $k_{zi}$ . If equivalent conversion of the controller in Fig. 4, we obtain Fig. 5. Then, substituting the system of Fig. 3 to Fig. 5, A2DOF digital integral type control system will be obtained as shown in Fig. 6. In Fig. 6, the parameters of the controller are as follows:

$$\begin{aligned} k_1 &= -f_1 - \frac{Gk_{zi}}{1 + H_1}, \quad k_2 = -f_2 \\ k_3 &= -f_3 \quad k_{ii} = G_i k_{zi}, \quad k_{ri} = Q_i \end{aligned} \quad (15)$$

#### 4. DIGITAL ROBUST VOLTAGE CONTROLLER

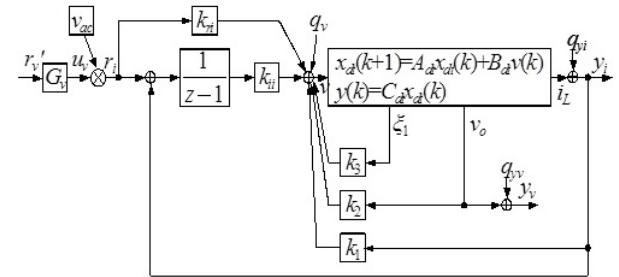

##### A. Addition of $u_v$ and $v_{ac}$ to $r_i$

Add the multiplier in front of the reference input  $r_i$  of the current control system. Let the inputs of the multiplier be  $v_{ac}$  and  $uv$  as shown in Fig. 7. In Fig. 7,  $v_{ac}$  is the absolute value of the input voltage  $v_{in}$  and  $uv$  is a new input. This addition is for making the inductor current  $i_L$  follow the AC voltage  $v_{ac}$ .

**Fig.5:** Equivalent conversion of the robust digital controller.

**Fig.6:** Approximate 2DOF digital integral type current control system.

**Fig.7:** Current control system added multiplier.

**B. Approximate controlled object for voltage controller**

The system of Fig. 7 becomes a controlled object for a voltage controller. Derive an approximated controlled object from this system for designing the voltage controller. In Fig. 7,  $u_v$  is a control input, and  $v_o = y_v$  is an output of the controlled object. When  $uv$  is set to  $u_v = G_v r_v'$ , the transfer function from  $r_v$  to  $v_o$  is as follows:

$$\begin{aligned} v_o &= \frac{(1 + H_2)}{(z + H_2)} \frac{(1 + H_1)}{(z + H_1)} \frac{(1 + p_{1i})}{(z + p_{1i})} \frac{(1 + p_{2i})}{(z + p_{2i})} \\ &\times \frac{(z - n_{1v})}{(1 - n_{1v})} \frac{(z - n_{2v})}{(1 - n_{2v})} r_v' = W_{ryv} r_v' \end{aligned} \quad (16)$$

where

$$G_v = \frac{1}{G_{uv}} \frac{a_{21} + a_{23}}{1 + a_{22}} + \frac{b_{21}}{G_{ui}}, \quad G_{ui} = \frac{1}{c_{dt}(I - A_{dt})^{-1} B_{dt}}$$

$G_{uv}$  is DC gain between  $u_v$  to  $v_o$ .  $n_{1v}$ ,  $n_{2v}$  are zeros of the transfer function from  $u_v$  to  $v_o$ .

In eq. (16)  $|H_2| \gg (|H_1|, |p_{1i}|, |p_{2i}|)$ , so the controlled object  $W_{ryv}$  for the voltage controller is approximated as

$$W_{ryv}(z) \approx W_{mv}(z) = \frac{1 + H_2}{z + H_2} \quad (17)$$

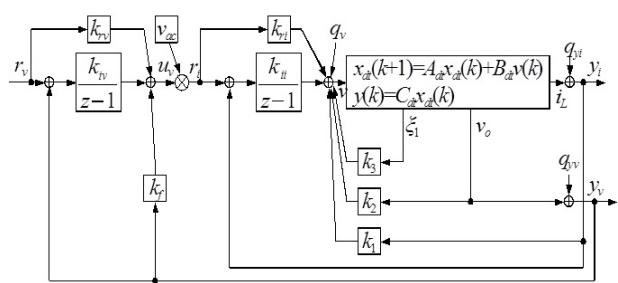

### C. Design method of A2DOF voltage controller

The inverse system  $W_{mv}^{-1}(z)$  and the filter  $K_v(z)$  are added to the system of eq. (15) like Fig. 4. Here  $K_v(z)$  is as follows:

$$K_v(z) = \frac{k_{zv}}{z - 1 + k_{zv}} \quad (18)$$

In Fig. 4,  $r_i, y_i, Q_i, q_v, q_{yi}, K_i, W_{ryi}, W_{mi}^{-1}$ , and  $W_{Qyi}$  are replaced with  $r_v, y_v, Q_v, q_v, q_{yv}, K_v, W_{ryv}, W_{mv}^{-1}$ , and  $W_{Qyv}$ , respectively. Then the transfer functions between  $r_v - y_v$ ,  $q_v - y_v$  and  $q_{yv} - y_v$  of the system like Fig. 4 are given by

$$y_v \approx \frac{1 + H_2}{z + H_2} r_v \quad (19)$$

$$y_v \approx \frac{z - 1}{z - 1 + k_{zv}} W_{Qv y_v}(z) Q_v \quad (20)$$

The A2DOF digital integral type control system will be obtained from the equivalent conversion of the controller like Fig. 4 as shown in Fig. 8. All specifications will be satisfied with only one controller of Fig. 7.

**Fig.8:** Approximate 2DOF digital integral type control System including the current controller and the voltage controller.

In Fig. 8, the parameters of the voltage controller are as follows:

$$k_f = -\frac{G_v k_{zv}}{1 + H_2}, k_{iv} = G_v k_{2v}, k_{rv} = G_v \quad (21)$$

## 5. EXPERIMENTAL STUDIES

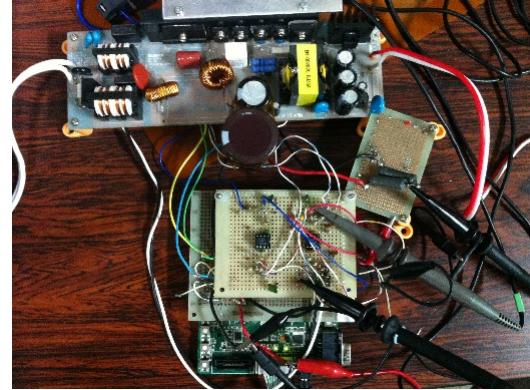

All experimental setup system is shown in Fig. 8. A microcontroller (RX62T) from Renesas Electronics is used for the digital controller. Three digital controllers for the current, voltage and DC-DC buck converter load were implemented on 1 Micro Controller.

**Fig.9:** Experimental setup system.

The A2DOF controllers for the interleaved PFC boost converter are designed at Operating Point shown in Fig.2. The design parameters of the A2DOF current control system have been determined as

$$H_1 = -0.45 \quad H_2 = n_{1i} = -0.9999 \quad H_3 = -0.2291 \\ k_{zi} = 0.4 \quad k_{zv} = 0.1 \quad (22)$$

Then the controller parameters become as

$$k_1 = -70.41 \quad k_2 = 0.6946 \quad k_3 = -16.17 \quad k_{ii} = 11.94 \\ k_{ri} = 4.776 \quad k_f = -36.83 \quad k_{iv} = 0.0051 \quad k_{rv} = 0.0005 \\ (23)$$

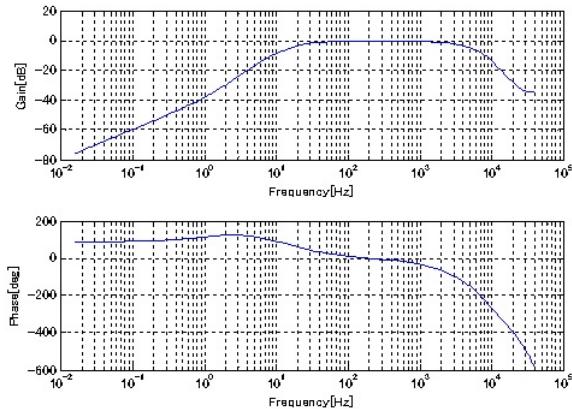

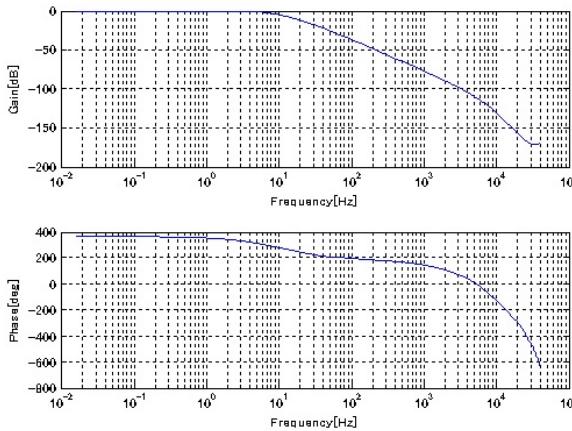

From these parameters the gain and phase characteristics of the current control system is shown in Fig. 10. The control bandwidth about 5kHz is attained. The gain and phase diagram of the voltage control system is shown in Fig. 11. The control bandwidth about 10Hz is attained.

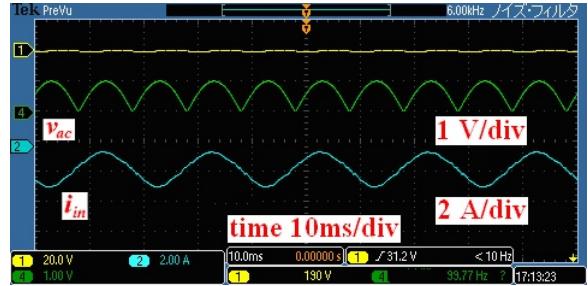

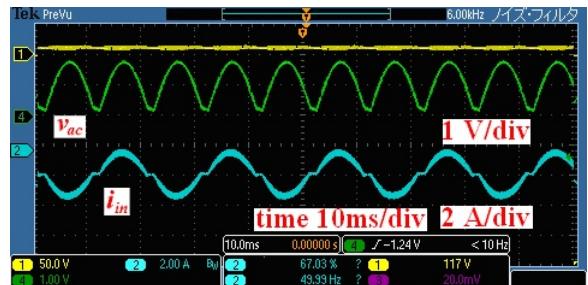

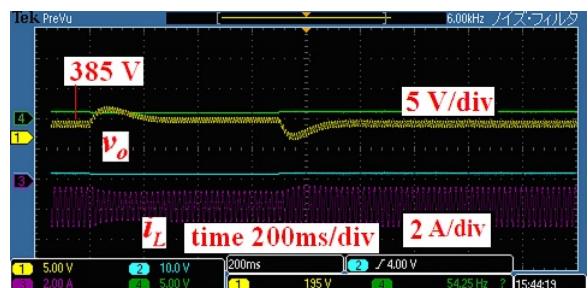

The experiment result of the steady state using the proposed controller is shown in Fig. 12. The input current waveform and the phase are almost same as the input voltage, and the power factor (PF) at full load is 0.99. The experiment result of the steady state using the conventional analog IC controller is shown in Fig. 13, and the power factor (PF) at full load is 0.97 because the input current waveform is distorted more than the one in Fig. 10 near at the zero cross point. That is, the proposed controller makes harmonic reduce. The experiment result of load sudden change using the proposed controller is shown in Fig. 14. The output voltage variation in sudden load

**Fig.10:** The gain and phase characteristics of the current control system.

**Fig.11:** The gain and phase characteristics of the voltage control system.

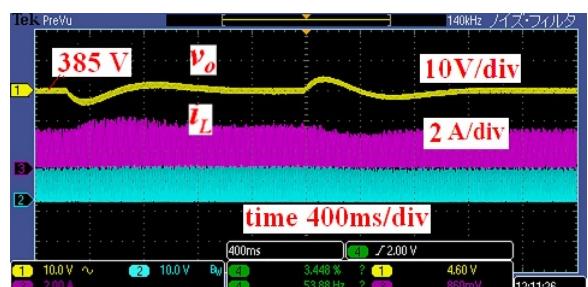

change is less than 6[V](1.56[%] of  $v_o$ ). And the experiment result of load sudden change using the conventional analog IC controller is shown in Fig. 15. The output voltage variation in sudden load change is less than 10[V](2.60[%] of  $v_o$ ). It turns out that the output voltage regulation of the proposed controller is better than the conventional analog IC controller. As a result, it turns out that proposed method is effective practically.

## 6. CONCLUSION

In this paper, the concept of the digital controller which attains good robustness for the interleaved PFC boost converter with DC-DC converter load was given. The proposed digital controller was implemented on the microprocessor. The PFC boost converter built-in this microprocessor was manufactured. It was shown from experiments that the digital controller which combined two A2DOF can suppress the variations of the step responses at load change and

**Fig.12:** Experimental result using the proposed A2DOF current controller and voltage controller,  $PF=0.99$ .

**Fig.13:** Experimental result using the conventional analog IC controller,  $PF=0.97$ .

**Fig.14:** 14 Experimental results of sudden load change from  $RL=10[\Omega]$  to  $5[\Omega]$  and reverse using the proposed A2DOF controller.

**Fig.15:** Experimental results of sudden load change from  $RL=10[\Omega]$  to  $5[\Omega]$  and reverse using the conventional IC controller.

the output voltage variations at sudden load changes while attaining the high power factor and the low harmonic. This fact demonstrates the usefulness and practicality of our proposed method. A future subject is checking experimentally the change of the output voltage when the input voltage is changed.

## References

- [1] L. Rossetto, G. Spiazzi, and P. Tenti, "Control Techniques for Power Factor Correction Converters, *Proc. PEMC94*, pp.1310-1318, 1994.

- [2] M. Xie, "Digital Control For Power Factor Correction, *Unpublished masters thesis, Virginia Polytechnic Institute and State University*, 2003.

- [3] E. D. Bolat, K. Erkan, S. Postalcioglu, "Using Current Mode Fuzzy Gain Scheduling Of PI Controller for UPS Inverter, *IEEE EUROCON 2005*, pp1505-1508, 2005.

- [4] M. Fu and Q. Chen, "A DSP Based Controller for Power Factor Correction (PFC) in a Rectifier Circuit, *IEEE APEC 2001*, pp.144-149, 2001.

- [5] K. De Gusseme, D. M. Van de Sype and J. A. A. Melkebeek, "Design Issues for Digital Control of Boost Power Factor Correction Converters, *IEEE ISIE 2002*, pp.731-736, 2002.

- [6] W. Zhang, G. Feng, Y. Liu and B. Wu, "A Digital Power Factor Correction (PFC) Control Strategy Optimized for DSP, *IEEE Transactions on Power Electronics*, Vol. 19, No. 6, pp.1474-1485, 2004.

- [7] E. Figueres, J. M. Benavent, G. Garcera and M. Pascual, "A Control Circuit With Load-Current Injection for Single-Phase Power-Factor-Correction Rectifiers, *IEEE Transactions on Industrial Electronics*, Vol. 54, No. 3, pp.1272-1281, 2007.

- [8] A. de Castro, P. Zumel, O. Garcia, T. Riesgo and J. Uceda, "Concurrent and Simple Digital Controller of an AC/DC Converter With Power Factor Correction Based on an FPGA, *IEEE Transactions on Power Electronics*, Vol. 18, No. 1, pp.334- 343, 2003.

- [9] S. Buso, P. Mattavelli, L. Rossetto and G. Spiazzi "Simple Digital Control Improving Dynamic Performance of Power Factor Preregulators, *IEEE Transactions on Power Electronics*, Vol. 13, No. 5, pp.814-823, 1998.

- [10] K. Higuchi, K. Nakano, T. Kajikawa, E. Takegami, S. Tomioka, K. Watanabe, "A New Design of Robust Digital Controller for DC-DC Converters, *IFAC 16<sup>th</sup> Triennial World Congress*, (CDROM), 2005.

- [11] K. Higuchi, E. Takegami, K. Nakano, T. Kajikawa, S. Tomioka, "Digital Robust Control for DC-DC Converter with Second- Order Characteristics, *ECTI-CON'2009*, pp.161-169, 2009.

- [12] S. Sasaki, and H. Watanabe, "Analysis of Multiple Operating Points for Dynamical Control of

Switching Power Converters, *IEIC Technical Report*, pp.33-38, 2005.

**Yuki Satake** received Master degree of School of Knowledge Science from Japan Advanced Institute of Science and Technology (JAIST), Ishikawa, Japan in 2009. From 2004 He is senior managing director and CTO at Sanshin Electric Co., Ltd.

**Hitoyuki Furuya** received a bachelor's degree from Teikyo Heisei University, Japan in 2011. From 1995, He is an Engineer for Development and Design of switching power supply at Sanshin electro Co., Ltd.

**Yohei Mochizuki** is a Master course 2<sup>nd</sup> year student of Graduate school in The University of Electro-Communications, Chofu, Japan. He is studying Power electronics and Control engineering, especially control of switching power supply.

**Yuji Fukaishi** received Master Eng. degree from The university of electro-communications, Chofu, japan, in 2011. From 2013, He is an Engineer, for Development and Design of switching power supply at Sanshin electro Co., Ltd.

**Kohji Higuchi** received his Ph.D. degree from Hokkaido University, Sapporo, Japan in 1981. In 1980 he joined the University of Electro-Communications, Tokyo, Japan, as an Research Associate, where he became an Assistant Professor in 1982 and currently an Associate Professor in the Dept. of Mechanical Engineering and Intelligent Systems, Electronic Control System Course. His interests include Power Electronics, Control Engineering and Digital Signal Processing. He is a member of IEEE, IEICE, SICE and IEEJ.

**Kosin Chamnongthai** currently works as professor at Electronic and Telecommunication Engineering Department, Faculty of Engineering, King Mongkut's University of Technology Thonburi (KMUTT), and also serves as editor of ECTI e-magazine, and assoc editor of ECTI-CIT Trans since 2011 until now. He served as assoc editor of ECTI-EEC Trans during 2003-2010, associate editor of ELEX (IEICE Trans) during 2008-2010, and chairman of IEEE COMSOC Thailand during 2004-2007.

He has received B.Eng. in Applied Electronics from the University of Electro-communications, Tokyo, Japan in 1985, M.Eng. in Electrical Engineering from Nippon Institute of Technology, Saitama, Japan in 1987 and D.Eng. in Electrical Engineering from Keio University, Tokyo, Japan in 1991. His research interests include image processing, computer vision, robot vision, and signal processing. He is a senior member of IEEE, and a member of IPS, TRS, IEICE, TESA, ECTI, and EEAAT.