# Low Power Despreader using Dynamic Reconfigurable Architecture for Multicarrier CDMA with Two-Dimensional Spreading and Variable Spreading Factor

Takayuki Sugawara<sup>1</sup> and Yoshikazu Miyanaga<sup>2</sup>, Non-members

#### ABSTRACT

In this paper, we propose a dynamic reconfigurable architecture of a despreader for Multicarrier code division multiple access (CDMA) with two-dimensional spreading and variable spreading factor. The spreading factors in the time and frequency domains are varied according to cell configuration, channel load, and propagation channel conditions in the system. The structure of the proposed despreader is dynamically changed with spreading factors. Following this structure, optimum parallel and pipeline processing are achieved. The proposed despreader reduces the power consumption by 60% compared with the basic one.

**Keywords**: low power circuit, dynamic reconfiguration, despreader, Multicarrier CDMA

#### 1. INTRODUCTION

Recently, there are various researches of the next generation mobile communications (4G) to establish broadband packet transmission with a maximum data rate exceeding 100Mbit/s [1]-[4]. In 4G system, the seamless deployment of wireless access employing one air interface is required in both multi-cell and isolated-cell environments. Multicarrier CDMA, which is examined to be used in 4G system, is based on a combination of orthogonal frequency division multiplexing (OFDM) signaling and CDMA technique.

The Multicarrier CDMA schemes are mainly categorized into three groups. The first group spreads the original data in the frequency domain [5],[6]. The second group spreads the original data in the time domain [7]. The third group spreads the original data in both the frequency and time domains [8]. In addition, the Multicarrier CDMA with variable spreading factor, which changes the spreading factor cor-

responding to the cell structure, channel load, radio link conditions and radio link parameters, has been proposed [9]. Although several communication methods of the Multicarrier CDMA with two-dimensional spreading and variable spreading factor have been examined [10]-[12], its hardware design has hardly been discussed. However, it is important to design a small size and a low power consumption circuit when the Multicarrier CDMA is mounted on the mobile terminal such as the cellular phone.

In the Multicarrier CDMA with two-dimensional spreading and variable spreading factor, the module structure that is quit different from a conventional system is a despreader since both spreading factors in the frequency and time domains are changed adaptively. Although the matched filter is usually used for despreading in the direct sequence CDMA [13], we consider that the sliding correlator can process it in the Multicarrier CDMA. In this paper, the sliding correlator is modified for the two-dimensional spreading. Furthermore, the despreader is designed with low power consumption using parallel and pipeline architecture. We have already proposed a dynamic reconfigurable despreader that changes the structure according to the spreading factor [14]. The proposed despreader in [14] can achieve parallelization and pipelining. This paper explains a circuit structure of the proposed despreader, and evaluates the area and the power consumption of the designed cir-

### 2. MULTICARRIER CDMA WITH TWO-DIMENSIONAL SPREADING AND VARI-ABLE SPREADING FACTOR

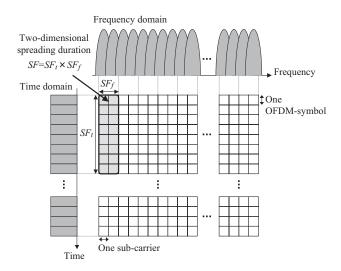

In the Multicarrier CDMA with two-dimensional spreading and variable spreading factor, the spreading factors in the time and frequency domains, i.e.  $SF_t$  and  $SF_f$ , are varied according the cell structure in order to achieve higher link capacity in both multi-cell and isolated-cell environments. The configuration of the two-dimensional spreading is shown in Fig.1. One data symbol is spreaded into  $SF_t$  successive OFDM-symbols and  $SF_f$  successive sub-carriers. A total spreading factor SF is  $SF_f \times SF_t$ .

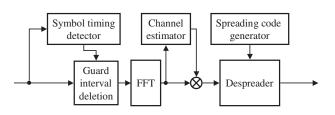

Fig.2 shows the baseband processing of the receiver for despreading. The symbol timing is detected and

Manuscript received on May 15, 2006.

<sup>&</sup>lt;sup>1</sup>The author is with the Graduate School of Engineering, Hokkaido University, Kita 13 Nishi 8, Kitaku, Sapporo-shi, Hokkaido, 060–8628 Japan; E-mail: taka@ice.eng.hokudai.ac.jp

<sup>&</sup>lt;sup>2</sup>The author is with the Graduate School of Information Science and Technology, Hokkaido University, Kita 14 Nishi 9, Kita-ku, Sapporo-shi, Hokkaido, 060–0814 Japan; E-mail: miya@ist.hokudai.ac.jp

Fig.1: Multicarrier CDMA with two-dimensional spreading and variable spreading factor.

Fig.2: Baseband processing at receiver.

the received signals are separated into sub-carrier sequences using Fast Fourier Transform (FFT). After the channel variation of each sub-carrier is compensated, the despreader calculates the correlation between equalization data and spreading code from the spreading code generator.

## 3. STATEMENT OF PROBLEM

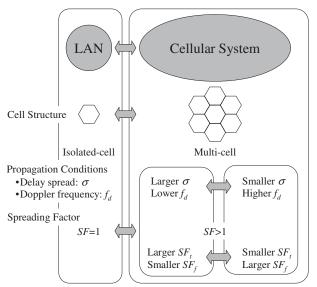

A network system which adapts to both wireless LAN and cellular system can sufficiently be constructed by implementing a variable spreading factor (Fig.3). For example, the Multicarrier CDMA performs the same processing as OFDM used in conventional wireless LAN when SF = 1. On the other hand, since the cellular system is under multicell environment, each cell is identified by multiplexed code where SF is set to be greater than 1. Furthermore, the transmission quality can be improved by changing  $SF_t$  and  $SF_f$  according to the propagation condition [11]. When delay spread  $\sigma$  is large, frequency selectivity fading becomes remarkable. In addition, different amplitudes and phases are influenced on each sub-carrier. Accordingly the orthogonality among the code-multiplexed channels in the frequency domain is destroyed. In this case, smaller  $SF_f$  should be employed. When Doppler frequency  $f_d$  is large, time fluctuation of fading becomes remarkable. In addi-

Fig.3: Concept of wireless network with variable spreading factor.

tion, different amplitudes and phases are influenced on each OFDM symbol. Accordingly the orthogonality in the time domain is easily destroyed. In this case, smaller  $SF_t$  should be employed.

Let us consider the situation of mobile wireless LAN. When a user uses his/her system in a room, it may be enough to use conventional OFDM. In this case, SF in the Multicarrier CDMA becomes 1. Once a user moves to cellular environment of Fig.3 with this system, SF should be controlled. Even if the system is used at the fixed location in outside,  $SF_t$  should be set large. When a user uses the system in automobile for example,  $SF_f$  should be set large.

For hardware design, the mount of (1) microprocessor or digital signal processor (DSP), (2) field programmable gate array (FPGA) or (3) application specific integrated circuit (ASIC), is considered. In the use of microprocessor and DSP, the processing can be changed by software, but the processing performance is insufficient to achieve high transmission rate. In the use of FPGA, the composition of the logical circuit can be freely programmed. The circuit structure is changed suitably according to the spreading factor. However, the transmission rate may decrease when the spreading factor is rapidly changed. This is based on a long time for changing the circuit structure. Therefore ASIC is designed in this paper. The proposed ASIC has high processing performance and instantaneously adjusts to the change of the spreading factor.

# 4. DESPREADER FOR TWO-DIMENSIONAL SPREADING AND VARIABLE SPREADING FACTOR

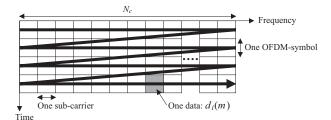

As shown in Fig.2, the output of FFT is input to the despreader after the channel equalization. Since the Multicarrier CDMA has many sub-carriers and the real time processing is required, it is suitable to use a pipeline FFT processor. The pipeline FFT processor produces a serial output. It outputs one datum at every one cycle [15]. Fig.4 shows the data flow of an input in a despreader where  $d_i(m)$  denotes equalization data of the  $i = 0, 1, \dots, N_c - 1$ -th sub-carrier at the m (= 0, 1, 2, ...)-th OFDM-symbol.  $N_c$  denotes the number of sub-carriers. If  $d_i(m)$  is fed into the despreader at a cycle,  $d_{i+1}(m)$  is input into the despreader at the next cycle. This process continues in frequency domain until  $d_{N_c-1}(m)$  is finally fed into. The m+1-th OFDM-symbol starting with  $d_0(m+1)$ is input into the despreader at the next.

Fig.4: Data flow of input into despreader.

After spreading, the data to be transmitted  $s_i(m)$  is given by

$$s_{i}(m) = x(k)c_{j}(n),$$

$$k = \left[\frac{i}{SF_{f}}\right] + \left[\frac{m}{SF_{t}}\right]\frac{N_{c}}{SF_{f}}$$

$$j = \operatorname{mod}(i, SF_{f})$$

$$n = \operatorname{mod}(m, SF_{t})$$

$$(1)$$

where x(k) denotes the data to be transmitted before spreading, and  $c_j(n)$  denotes the spreading code. [X] rounds the elements of X to the nearest integers where  $[X] \leq X$ . mod (Y, Z) is the modulus after Y/Z. In the despreader, the following equation is applied.

$$y(k) = \sum_{n=0}^{SF_t - 1} \sum_{j=0}^{SF_f - 1} d_{f+j}(t+n)c_j(n).$$

(2)

$$f = \text{mod}(k, N_c/SF_f)$$

$$t = [kSF_f/N_c]$$

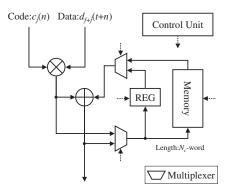

As written above, the despreader processes the non-successive input data in the Multicarrier CDMA with two-dimensional spreading. Accordingly this paper, the simple sliding correlator is used for two-dimensional spreading as shown in Fig.5. It is considered as a basic despreader.

Fig.5: Structure of basic despreader.

The frequency domain despreading is processed by connecting the adder and the register as loopback structure in Fig.5. The memory is used to hold intermediate result for the time domain despreading. The maximum capacity of the memory is  $N_c$ -words. The actually used area is  $N_c/SF_f$ -words.

#### 5. LOW POWER CONSUMPTION DE-SPREADER

Both parallelization and pipelining of circuit are an effective way of constructing low power architecture [16]. However it is difficult to make a parallel and pipeline despreader of unique circuit structure since the spreding factor SF is changed adaptively in the Multicarrier CDMA that utilizes variable spreading factor. The proposed despreader achieves ideal parallelization and pipelining according to the spreading factor by using multiplexers. Moreover in the proposed despreader, the memory is divided into some small size banks.

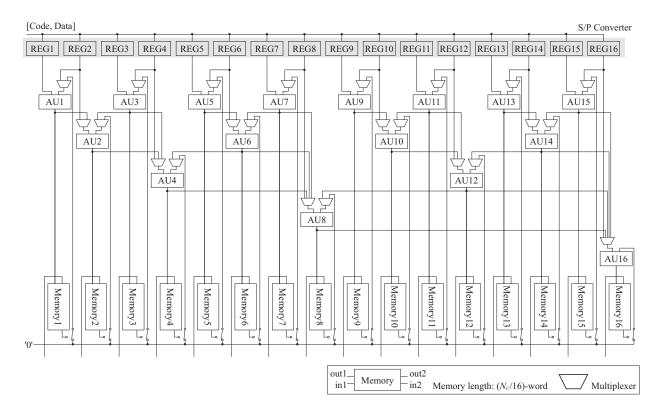

An adder network shown in Fig.6 changes connection pattern between add units (AUs) according to the spreading factor in the frequency domain, i.e.  $SF_f$ . In the top part of the figure,  $SF_{max}$  registers are arranged where  $SF_{max}$  denotes the maximum  $SF_f$ . The datum is sequentially fed into the adder network. Using these registers, all data are arranged into parallel. These registers work as a serial/parallel (S/P) converter. The adder network consists of  $SF_{max}$  AUs, and each AU outputs to the memory. The capacity of the memory of the proposed despreader is  $N_c/SF_{max}$ -words. This memory is dual-port. One port is used to hold the output from AU and then to output the calculation result of the adder network. The other port is connected to AU for a loopback structure.

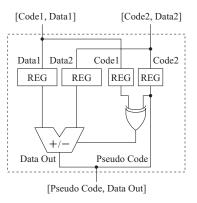

The AU consists of four registers, one exclusive-OR gate and one adder-subtracter as shown in Fig.7. The AU receives as input two spreading codes (Code1, Code2) and two equalization data (Data1, Data2). The outputs of the AU are pseudo code and calculation result (Data Out). Each register holds input data at every  $SF_{max}$  cycles. The spreading code used in the Multicarrier CDMA is Walsh-Hadmard

**Fig.6:** Structure of adder network ( $SF_{max} = 16$ ).

code whose value is '+1' or '-1'. Therefore, multiplication between spreading code and equalization datum mentioned in Eq.(2) can be realized to change sign of equalization datum if spreading code is '-1'. The adder-subtracter calculates Data2±Data1. Addition or subtraction is selected according to the output of the exclusive-OR gate. If both Code1 and Code2 are '+1', then addition is selected. The pseudo code thus becomes '+1'. If Code1 and Code2 are '-1' and '+1', respectively, then subtraction is selected. The pseudo code thus becomes '+1'. If Code1 and Code2 are '+1' and '-1', respectively, then subtraction is selected. The pseudo code thus becomes '-1'. The AU accordingly calculates -(Data2-Data1)=Data1-Data2. If both Code1 and Code2 are '-1', then addition is selected. The pseudo code thus becomes '-1'.

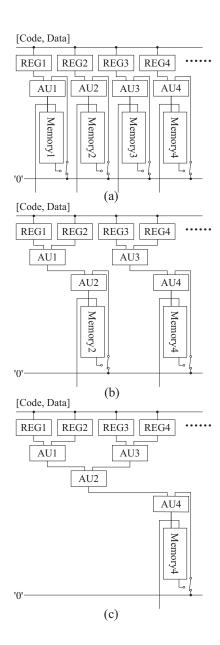

Input data of AU are controlled by multiplexer according to several  $SF_f$ . In the case of  $SF_f = 1$ , each AU is composed in parallel (Fig.8(a)).  $c_j(n)$  and  $d_{f+j}(t+n)$  are input into Code1 and Data1 shown in Fig.7, respectively. In the case of  $SF_f = 2$ , each AU is composed in two pipeline stages and  $SF_{max}/2$  parallel lines (Fig.8(b)). AU of the first pipeline stage processes the despreading in the frequency domain. AU of the second pipeline stage processes the time domain despreading. In the case of  $SF_f = 4$ , each AU is composed in three pipeline stages and  $SF_{max}/4$  parallel lines (Fig.8(c)).

To summarize, the adder network is designed to

Fig. 7: Structure of add unit.

form the alignment of  $SF_f$  AUs in  $\log_2 SF_f + 1$  pipeline stages in  $SF_{max}/SF_f$  parallel lines. AUs which are arranged from the first to  $\log_2 SF_f$ -th pipeline stages process the despreading in the frequency domain. The time domain despreading is processed by AU of the last pipeline stage and memory.

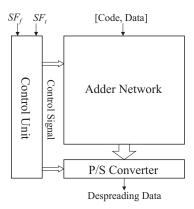

Fig.9 shows block diagram of the proposed low power despreader. The control unit generates signals controlling each module. Despreading data is selected from outputs of all memories of the adder network by the parallel/serial (P/S) converter according to the control signal.

**Fig.8:** Connection pattern of adder units (a) $SF_f = 1(b)SF_f = 2(c)SF_f = 4$ .

#### 6. EVALUATION OF DESIGNED CIRCUIT

Both the circuits of the basic despreader and the proposed low power despreader have been designed with Verilog-HDL and synthesized to TSMC  $0.25\mu m$  standard cell library with Synopsys Design Compiler. Table 1 shows the design parameters. Since the number of sub-carriers is 768 and the OFDM-symbol duration is  $9.259\mu sec$ , the cycle of data input to despreader is 12.1nsec. Accordingly, these despreaders are followed by gate level simulations, run at 82MHz. Synopsys Power Compiler is used for power analysis.

Table 2 shows the number of gates. Since the memory is divided into sixteen in the proposed despreader, the number of peripheral circuits of the memory increases more than the basic despreader. Therefore,

Fig.9: Block diagram of low power despreader.

**Table 1:** Design parameters.

| 768                     |  |  |  |  |  |  |

|-------------------------|--|--|--|--|--|--|

| 1024                    |  |  |  |  |  |  |

| 2, 4, 8, 16             |  |  |  |  |  |  |

| $9.259\mu \mathrm{sec}$ |  |  |  |  |  |  |

| 52 OFDM-symbols         |  |  |  |  |  |  |

| (Data:48, Pilot:4)      |  |  |  |  |  |  |

| 12bit                   |  |  |  |  |  |  |

| 1bit                    |  |  |  |  |  |  |

| 2.5V                    |  |  |  |  |  |  |

|                         |  |  |  |  |  |  |

Table 2: Number of Gates.

| Basic despreader    | 24646   |

|---------------------|---------|

| (Memory)            | (23478) |

| Proposed despreader | 93718   |

| (Memory)            | (82630) |

the number of total memory gates increases by about 3.5 times. The parallelization and the pipelining also increase the number of the other circuits. The total gates of the proposed circuit increases by nearly 4 times.

Table 3 shows the power consumption. Since in the case of  $SF_t = 1$ , the memory is not used in the basic despreader, the other circuits, i.e. the multiplier, the adder, the register, multiplexers and the control unit, require the power of 63mw. The clock frequency of proposed despreader is 1/16 compared with the basic one. It reduces the power consumption by 60% or more in the case of  $SF_f = 16$  and  $SF_t = 1$ . In the case of  $SF_t \geq 2$ , the number of accesses to the memory of the basic despreader increases as  $SF_t$  becomes large or  $SF_f$  becomes small. As a result, the power consumption increases. On the other hand, the power consumption is constant at any  $SF_t$  in the proposed despreader if  $SF_f$  is the same. In the case of  $SF_f = 1$ and  $SF_t = 2$ , the reduction of power consumption is the least. The proposed despreader requires 13% less power consumption than the basic one.

Table 4 shows comparison of the proposed despreader with the conventional digital matched filter

**Table 3:** Power consumption[mW@82MHz].

| / \  | ъ.    | 1        | 1 🙃   |

|------|-------|----------|-------|

| (a.) | Basic | despread | 1er(W |

|             | $SF_f = 1$ | $SF_f = 2$ | $SF_f = 4$ | $SF_f = 8$ | $SF_f = 16$ |

|-------------|------------|------------|------------|------------|-------------|

| $SF_t = 1$  |            | 63.2       | 63.0       | 62.8       | 62.7        |

| $SF_t = 2$  | 93.1       | 77.6       | 69.8       | 66.0       |             |

| $SF_t = 4$  | 110.3      | 85.2       | 73.3       |            |             |

| $SF_t = 8$  | 119.3      | 89.2       |            |            |             |

| $SF_t = 16$ | 123.9      |            |            |            |             |

(b) Proposed despreader

|             | $SF_f = 1$ | $SF_f = 2$ | $SF_f = 4$ | $SF_f = 8$ | $ SF_f = 16 $ |

|-------------|------------|------------|------------|------------|---------------|

| $SF_t = 1$  |            | 50.6       | 35.6       | 28.2       | 24.4          |

| $SF_t = 2$  | 80.7       | 50.8       | 35.7       | 28.2       |               |

| $SF_t = 4$  | 80.3       | 50.5       | 35.6       |            |               |

| $SF_t = 8$  | 80.1       | 50.4       |            |            |               |

| $SF_t = 16$ | 80.0       |            |            |            |               |

**Table 4:** Comparison of proposed despreader with conventional DMF.

|                     | technol-           | supply  | code length  | input     | fre-   | power   | normalized         |

|---------------------|--------------------|---------|--------------|-----------|--------|---------|--------------------|

|                     | ogy                | voltage | $(SF_{max})$ | data bits | quency | [mW]    | power              |

|                     | $[\mu \mathrm{m}]$ | [V]     | [chip]       |           | [MHz]  |         | $[\mu W/MHz/chip]$ |

| Proposed            | 0.25               | 2.5     | 16           | 12        |        | Table 3 |                    |

| S/P Converter       |                    |         |              |           | 82     | 3.0     | 2.3                |

| AUs                 |                    |         |              |           | 5.2    | 9.0     | 108                |

| Conventional[13]    | 0.18               | 1.6     | 256          | 6         |        | 9.3     |                    |

| Reception Registers |                    |         |              |           | 15.6   | 0.4     | 0.1                |

| CCB                 |                    |         |              |           | 15.6   | 8.7     | 2.2                |

(DMF) presented in [13]. The proposed despreader has different function from the conventional DMF, i.e., the conventional DMF cannot process the time domain despreading. Moreover, the design parameters, such as the CMOS technology, the supply voltage and the operating frequency, are different. Therefore the proposed despreader cannot easily be compared with the conventional DMF. For rough comparison, the power consumption normalized by the code length and the operating frequency is attached to the same function modules of each circuit. The reception registers and the correlation calculating block (CCB) of the conventional DMF correspond to the S/P converter and the AUs of the proposed despreader, respectively. The power consumption of both the S/P converter and the AUs are constant, regardless of SF.

As the S/P converter is designed by the same architecture with the reception registers, the CMOS technology, the supply voltage and the input data bits become the cause of the S/P converter requiring 23 times as much normalized power consumption as the reception registers. Therefore normalized power consumption of the S/P converter becomes  $0.1\mu W/MHz/chip$  if it is designed by the same parameter as the reception registers.

The AUs output summation of input data every 193.6nsec in the case of  $SF_f = 16$ , so its operating fre-

quency is 5.2MHz. The normalized power consumption increases by approximately 49 times compared to the CCB. The ratio of the normalized power consumption of the AUs to that of the CCB is larger than the ratio of the normalized power consumption of the S/P converter to that of the reception registers. The reason for such increase in ratio is that each AU contains registers to keep parallelization and pipelining regardless of SF.

### 7. CONCLUSIONS

This paper presents a low power despreader for the Multicarrier CDMA with two-dimensional spreading and variable spreading factor. In this Multicarrier CDMA system, the spreading factors in the time and frequency domains are changed according to communication circumstances. Since the structure of the proposed despreader is dynamically changed according to the spreading factor, it can achieve parallelization and pipelining in all the cases. Compared with the basic despreader, it realizes 13-60% power reduction.

#### ACKNOWLEDGEMENT

The authors would like to thank Research and Development Headquarters, Yamatake Corporation.

This work is supported by LSI Design and Education Center(VDEC), the University of Tokyo, and MO-SIS in collaboration with Synopsys, Inc. This work is supported in parts by Semiconductor Technology Academic Research Center(STARC), Project J-17.

#### References

- [1] F.Adachi, "Wireless Past and Future–Evolving Mobile Communications Systems-," IEICE TRANS, vol.E84-A, no.1, pp.55-60, Jan. 2001.

- [2] Suk YH, Yeung KH, "Challenges in the migration to 4G mobile systems," IEEE Comm Magazine, vol.41, no.12, pp.54-59, Dec. 2003.

- [3] Munoz M, Rubio CG, "A new model for service and application convergence in B3G/4G networks," IEEE Wireless Communications, vol.11, no.5, pp.6-12, Oct. 2004.

- [4] K.Imai, W.Takita, S.Kano, A.Kodate, "An Extension of 4G Mobile Networks towards the Ubiquitous Real Space," IEICE TRANS, vol.E88-B, no.7, pp.2700-2708, Jul. 2005.

- [5] K. Fazel, "Performance of CDMA/OFDM for mobile communication systems," Proc. IEEE ICUPC '93, pp.975-979, Oct. 1993.

- [6] A.Chouly, A.Brajel, S.Jourdan, "Orthogonal multicarrier techniques applied to direct sequence spread spectrum CDMA systems," Proc. IEEE GLOBECOM '93, pp.1723-1728, Nov. 1993.

- [7] V.M.DaSilva, E.S.Sousa, "Multicarrier orthogonal CDMA signals for quasi-synchronous communication systems," IEEE Journal on Selected Areas in Comm, vol.12, no.5, pp.842-852, Jun. 1994.

- [8] N.Maeda, H.Atarashi, S.Abeta, M.Sawahashi, "VSF-OFCDM Using Two-Dimensional Spreading and Its Performance," IEICE Technical Report, RCS2002-61, pp.59-64, May. 2002 [In Japanese].

- [9] H.Atarashi, S.Abeta, M.Sawahashi, "Variable Spreading Factor-Orthogonal Frequency and Code Division Multiplexing (VSF-OFCDM) for Broadband Packet Wireless Access," IEICE TRANS, vol.E86-B, no.1, pp.291-299, Jan. 2003.

- [10] H.Atarashi, N.Maeda, Y.Kishiyama, M.Sawahashi, "Performance of VSF-OFCDM with Two-Dimensional Spreading Prioritizing Time Domain Spreading," IEICE Technical Report, RCS2002-85, pp.61-66, Jun. 2002 [In Japanese].

- [11] N.Maeda, Y.Kishiyama, H.Atarashi, M.Sawahashi, "Variable Spreading Factor-OFCDM with Two Dimensional Spreading that Prioritizes Time Domain Spreading for Forward Link Broadband Wireless Access," IEICE TRANS, vol.E88-B, no.2, pp.487-498, Feb. 2005.

- [12] K.Hasegawa, R.Shimura, T.Ohno, N.Yoshimochi, I.Sasase, "OVSF Code Allocation and Two-stage Combining Method to reduce Inter-code Interference in OFCDM sys-

- tem," IEICE Technical Report, RCS2005-7, pp.1-6, Apr. 2005 [In Japanese].

- [13] T.Yamada, S.Goto, N.Takayama, Y.Matsushita, Y.Harada, Y.Harada, H.Yasuura, "Low-Power Architecture of a Digital Matched Filter for Direct-Sequence Spread-Spectrum System," IE-ICE TRANS, vol.E86-C, no.1, pp.79-88, Jan. 2003.

- [14] T.Suagawara, Y.Miyanaga, "Dynamic Reconfigurable Despreader for VSF-OFCDM," IEICE Technical Report, SIS2005-9, pp.49-52, Jun. 2005 [In Japanese].

- [15] S.He, M.Torkelson, "A New Approach to Pipeline FFT Processor," Proceedings of the 10th International Parallel Processing Symposium, pp.766-770, Apr. 1996.

- [16] A.P.Chandrakasan, S.Sheng, R.W.Brodersen, "Low-power CMOS digital design," IEEE J, Solid-State Circuits, vol.27, no.4, pp.473-484, Apr. 1992.

Takayuki Sugawara was born in Sapporo, Japan on 1978. He received the B.S. and M.S. degrees from Hokkaido University Sapporo, Japan, in 2000 and 2002, respectively. He is currently a doctoral student in Hokkaido University. His research interests are in the fields of Mobile Communications and LSI System Design. Mr. Sugawara is a member of the Institute of Electrical and Electronics Engineers (U.S.A.) and the Insti-

tute of Electronics, Information and Communication Engineers (Japan).

Yoshikazu Miyanaga was born in Sapporo, Japan, on December 20, 1956. He received the B.S., M.S., and Dr. Eng. degrees from Hokkaido University, Sapporo, Japan, in 1979, 1981, and 1986, respectively. He was a Research Associate at the Institute of Applied Electricity, Hokkaido University from 1983 to 1987, a lecturer of Electronic Engineering at Faculty of Engineering, Hokkaido University from 1987 to 1988 and an Asso-

ciate Professor of Electronic Engineering at Faculty of Engineering, Hokkaido University from 1988 to 1997. He is currently a Professor of Laboratory for Information Communication Network, Division of Media and Network Technologies at Graduate School of Information Science and Technology, Hokkaido University. His research interests are in the areas of digital signal processing, communication systems and parallel/pipelined VLSI system. Dr. Miyanaga is a member of the Institute of Electronics, Information and Communication Engineers (U.S.A.), the Institute of Electronics, Information and Communication Engineers (Japan) and the Acoustical Society of Japan.