## Grounded series RL-type lossy inductance simulator using G<sub>m</sub>-C

Sasitaporn Theingjit and Worapong Tangsrirat\*

Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok 10520, Thailand.

Received April 2016

Accepted June 2016

## Abstract

This paper presents the resistorless simulation of a grounded RL-type lossy inductor using only transconductance cells ( $G_m$  cells). The proposed circuit is created using eight MOS transistors and only one external grounded capacitor, resulting in a simple and compact structure as well as attractive for integration. The equivalent resistance value ( $R_{eq}$ ) and equivalent inductance value ( $L_{eq}$ ) can be adjusted separately by means of the external bias currents. Simulation results based on TSMC 0.35- $\mu\text{m}$  CMOS process parameters are given to verify the theory and their operations.

**Keywords:** Transconductance cell ( $G_m$ -cell), Grounded lossy inductance, RL circuit, Impedance simulator

## 1. Introduction

Actively simulated lossy grounded inductors are one of the important circuit elements in active network synthesis and design, especially in active filter and oscillator designs. This is due to the fact that the physical inductors are large and bulky. Moreover, their behaviors spread the magnetic energy, and cannot be adjusted electronically. For these reasons, a number of grounded lossy inductance similar topologies using various active building blocks were reported in the open literature [1-5]. However, each of the active circuit building block in circuit realizations typically involves a large number of employed transistors. Moreover, all of these simulators need an excessive number of external passive components.

The goal of this communication is to present a circuit configuration for simulating a grounded series RL-type lossy inductor based on using transconductance cells ( $G_m$ -cells) as fundamental active circuits. The proposed circuit contains eight MOS transistors and one external grounded capacitor. The resulting circuit has considerable advantages in compact structure, reducing cost and in fully integrated circuit design. The equivalent resistance and inductance values of the realized grounded inductor can be adjusted electronically and independently by changing the external bias currents. The performance verifications of the proposed circuit are performed by PSPICE simulation with TSMC 0.35- $\mu$ m CMOS process parameters.

## 2. Basic $G_m$ -cell realization

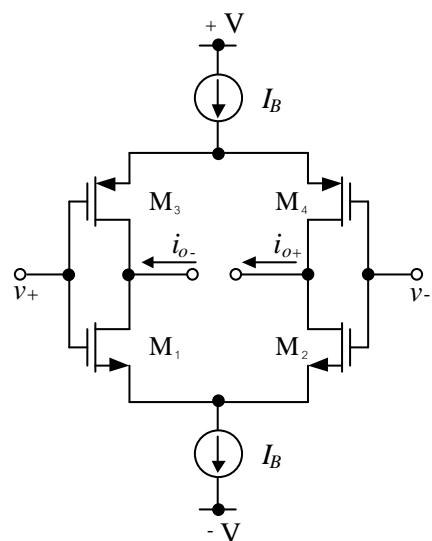

A particularly simple CMOS realization of the tunable  $G_m$  cell, which will be used as a fundamental circuit for implementing the proposed circuit, is shown in Figure 1. The circuit is mainly composed of two Arbel-Goldminz

transconductors [6], which its transconductance value can be approximately determined by:

$$G_m \equiv \left( \frac{g_{m1}g_{m2}}{g_{m1} + g_{m2}} \right) + \left( \frac{g_{m3}g_{m4}}{g_{m3} + g_{m4}} \right) \quad (1)$$

In equation (1),  $g_{mi} = [K_{n(p)}I_B]^{1/2}$  ( $i = 1, 2, 3, 4$ ) and  $K_{n(p)}$  is the transconductance parameter of NMOS (PMOS) transistor and  $I_B$  is an external DC bias current. It should be noted from eq.(1) that the  $G_m$ -value is electronically tunable by changing the bias current  $I_B$ .

**Figure 1** CMOS realization of the tunable  $G_m$ -cell

\*Corresponding author.

Email address: worapong.ta@kmitl.ac.th

doi: 10.14456/kkuenj.2016.96

### 3. Proposed grounded lossy inductance simulator

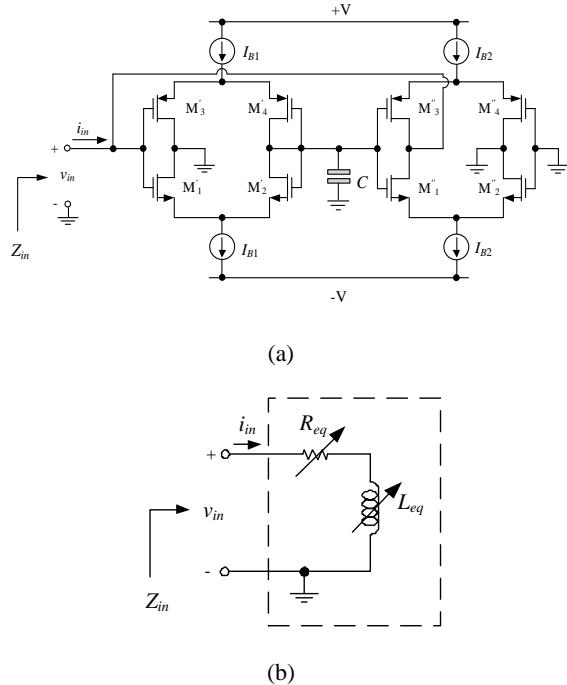

Figure 2 shows the simulation scheme for an electronically tunable grounded lossy inductor using only two  $G_m$ -cells of Figure 1 and one capacitor. The structure requires eight MOS transistors and only one grounded capacitor, resulting in a resistorless and canonical configuration. The input impedance of the circuit is found as:

$$Z_{in} = \frac{v_{in}}{i_{in}} = \frac{sC + G_{m1}}{G_{m1}G_{m2}} = \frac{1}{G_{m2}} + \frac{sC}{G_{m1}G_{m2}} = R_{eq} + sL_{eq} \quad (2)$$

where  $G_{mi}$  is the transconductance of the  $i$ -th  $G_m$ -cell ( $i = 1, 2$ ). Eq.(2) indicates that the proposed circuit of Figure 2 simulates the lossy inductor with the following equivalent resistance and inductance values:

$$R_{eq} = \frac{1}{G_{m2}} \quad (3)$$

and

$$L_{eq} = \frac{C}{G_{m1}G_{m2}} \quad (4)$$

This reveals that the value of  $R_{eq}$  can be adjusted electronically through  $G_{m2}$ , while the value of  $L_{eq}$  can be tuned by  $G_{m1}$  without affecting the  $R_{eq}$ .

**Figure 2** Proposed grounded series RL-type lossy inductance simulator circuit. (a) CMOS circuit implementation (b) equivalent behavior model

### 4. Computer simulations and discussions

The behaviors of the proposed grounded series RL simulator circuit in Figure 2 are demonstrated with PSPICE simulation results using TSMC 0.35- $\mu$ m CMOS process model parameters. The dimensions  $W(\mu\text{m})/L(\mu\text{m})$  of the MOS transistors were set to be 16.1/0.7 for  $M_1$ - $M_2$ , and 28/0.7 for  $M_3$ - $M_4$ . The supply voltages used were  $+V = -V = 1.5$  V.

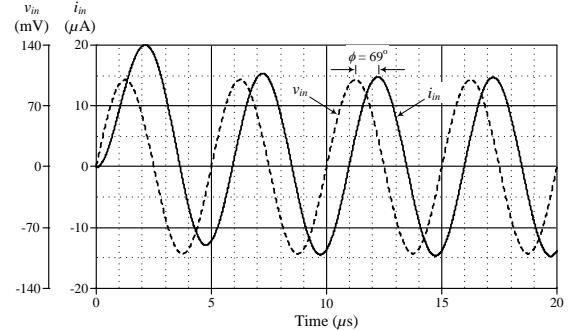

**Figure 3** Simulated waveforms for  $v_{in}$  and  $i_{in}$  of the simulator in Figure 2

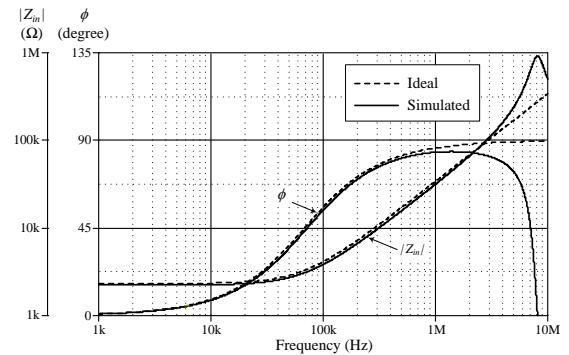

**Figure 4** Simulated frequency responses for magnitude ( $|Z_{in}|$ ) and phase ( $\phi$ ) of  $Z_{in}$  in Figure 2

To demonstrate the characteristic of the actively simulated grounded series RL circuit of Figure 2, the circuit was simulated and compared with the passive RL series circuit. In simulations, the component values were taken as :  $I_B = I_{B1} = I_{B2} = 50 \mu\text{A}$  ( $G_m = G_{m1} = G_{m2} \approx 0.43 \text{ mA/V}$ ) and  $C = 1 \text{ nF}$ , resulting in  $R_{eq} \approx 2.32 \text{ k}\Omega$  and  $L_{eq} \approx 5.41 \text{ mH}$ . The simulated  $v_{in}$  and  $i_{in}$  waveforms of the simulator circuit of Figure 2 with an input frequency of 200 kHz are shown in Figure 3. From the results, it can be measured that the phase difference ( $\phi$ ) between  $v_{in}$  and  $i_{in}$  is about  $69^\circ$ , which is in close correspondence with the calculated value equal to  $70^\circ$ . As far as the amplitude of the input current  $i_{in}$  in the time range of 0-5  $\mu$ s is concerned, it is well known that it mainly depends on the initial conditions (voltage across or current through one of the circuit capacitors), besides being dependent on the active device and on its biasing conditions. The ideal and simulated frequency responses of the simulator are also shown in Figure 4. Note that the simulator operates correctly along the frequency range approximately up to 2 MHz, where the percentage errors in the magnitude and phase responses are about 2.77% and 4.84%, respectively.

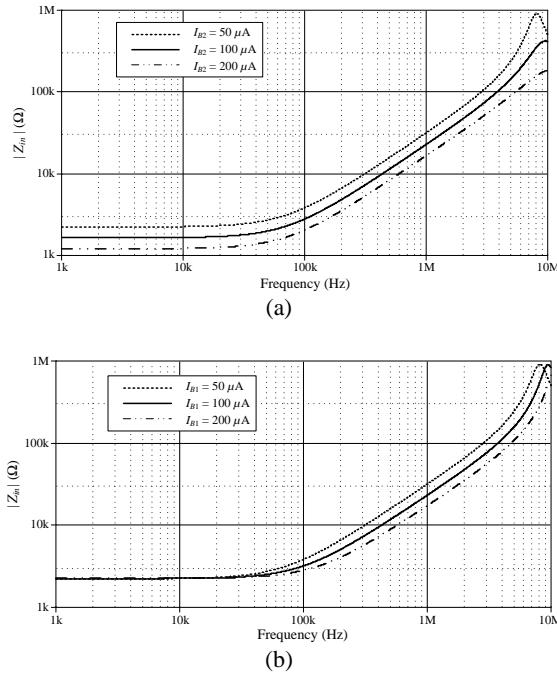

Figure 5 shows the frequency characteristics of the grounded series RL simulator circuit of Figure 2 for various biasing currents. In Figure 5(a), the simulated frequency responses with  $C = 1 \text{ nF}$ , and  $I_{B1} = 50 \mu\text{A}$  ( $G_{m1} = 0.43 \text{ mA/V}$ ) are plotted. In accordance with equations (1), (3) and (4), the simulations were performed by varying  $I_{B2} = 50 \mu\text{A}$  ( $G_{m2} \approx 0.43 \text{ mA/V}$ ),  $100 \mu\text{A}$  ( $G_{m2} \approx 0.6 \text{ mA/V}$ ), and  $200 \mu\text{A}$  ( $G_{m2} \approx 0.8 \text{ mA/V}$ ), in order to obtain  $R_{eq} \approx 2.32 \text{ k}\Omega$ ,  $1.67 \text{ k}\Omega$ , and  $1.25 \text{ k}\Omega$ , and  $L_{eq} \approx 5.41 \text{ mH}$ ,  $3.88 \text{ mH}$ , and  $2.91 \text{ mH}$ , respectively. Likewise, the results in Figure 5(b) were obtained by selecting :  $C = 1 \text{ nF}$ ,  $R_{eq} \approx 2.32 \text{ k}\Omega$ ,  $L_{eq} \approx 5.41 \text{ mH}$ ,  $3.88 \text{ mH}$ , and  $2.91 \text{ mH}$ , where  $I_{B2} = 50 \mu\text{A}$  ( $G_{m2} = 0.43 \text{ mA/V}$ ). The simulations were performed by setting:  $I_{B1} = 50 \mu\text{A}$ .

$\mu\text{A}$  ( $G_{m1} \geq 0.43 \text{ mA/V}$ ),  $100 \mu\text{A}$  ( $G_{m1} \geq 0.6 \text{ mA/V}$ ), and  $200 \mu\text{A}$  ( $G_{m1} \geq 0.8 \text{ mA/V}$ ), respectively. Also note that the simulation results are in close agreement with the predicted values, and confirm that the values of  $R_{eq}$  and  $L_{eq}$  can be adjusted electronically through  $G_{m2}$  and  $G_{m1}$ , respectively.

**Figure 5** Magnitude-frequency characteristics for the simulator of Figure 2 (a) with  $I_{B2}$ -tuning (b) with  $I_{B1}$ -tuning

## 5. Conclusions

This paper describes a grounded series RL lossy inductance simulator circuit with electronically tunable feature based on the use of the basic transconductance cells ( $G_m$ -cells) and only one grounded capacitor. The equivalent resistance and inductance values of the simulator can be adjusted electronically by changing bias currents of the  $G_m$ -cells. PSPICE simulation results verify the performances of the proposed circuit, which are in close agreement with the prediction analysis.

## 6. References

- [1] Kuntman H, Gulsoy M, Cicekoglu O. Actively simulated grounded lossy inductors using third generation current conveyors. *Microelectron J* 2000; 31:245-250.

- [2] Kacar F, Yesil A, Minaei S, Kuntman H, Positive/negative lossy/lossless grounded inductance simulators employing single VDCC and only two passive elements. *Int J Electron Commun (AEU)* 2014;68:73-78.

- [3] Yesil A, Kacar F. New DXCCII-based grounded series inductance simulator topologies. *IU-JEEE*. 20014;14:1785-1789.

- [4] Alpaslan H, Yuce E. Inverting CFOA based lossless and lossy grounded inductor simulators. *Circuits Syst Signal Process* 2015;34:3081-3100.

- [5] Pathak JK, Singh AK, Senani R. New canonic lossy inductor using a single CDBA and its application. *Int J Electron* 2015;103:1-13.

- [6] Arbel A F, Goldminz L. Output stage for current-mode feedback amplifiers, theory and applications. *Analog Integr Circ Sig Process* 1992;2:243-255.