# A fully differential full-wave rectifier using current conveyors \*

Adisak Monpapassorn <sup>1)</sup>

<sup>1)</sup> Assistant Professor, Department of Electronic Engineering, South-East Asia University, Bangkok 10160

Email: aone\_mon@hotmail.com

## Abstract

This work presents a fully differential full-wave rectifier using current conveyors. Both input and output signals of the proposed rectifier can be differential or single modes. The proposed rectifier consists of two current conveyors, a positive full-wave current rectifier, a negative full-wave current rectifier and two MOS-resistors. The proposed rectifier uses all MOS structure. Simulation results from the layout in a 0.5  $\mu$ m MOS technology of AMI are obtained by using the level 49 model through MOSIS. The results showing the operation of the proposed rectifier at the frequencies of 1 MHz and 100 MHz are included.

**Keywords:** rectifier, CMOS circuit

---

\* Original manuscript submitted: November 1, 2004 and Final manuscript received: November 26, 2004

## Introduction

Rectifiers are extensively used in wattmeters, AC voltmeters, RF demodulators, piecewise linear function generators, and various nonlinear analog signal-processing circuits. The operation of a simple diode rectifier is limited by the threshold voltage of a diode, approximately 0.3 V for a germanium diode and 0.7 V for a silicon diode, thus the simple diode rectifier is used only in some applications in which the precision in a range of the threshold voltage is insignificant, such as radio frequency demodulators and DC voltage supply rectifiers. However, for applications requiring accuracy in the range of the threshold voltage, the simple diode rectifier cannot be used. This can be overcome by using integrated circuit (IC) rectifiers instead.

In the past, many integrated circuit full-wave rectifiers have been proposed. Most of the integrated circuit full-wave rectifiers proposed do not operate in a fully differential mode (both input and output being a single mode, or input as the differential mode but output as the single mode). In the single mode, one of two inputs has to be grounded, causing that the rectifier cannot apply to a differential input to not refer to ground. Additionally, one of two outputs must also be grounded; this results in that the rectifier cannot supply the output to a floating load or a floating input of a next circuit.

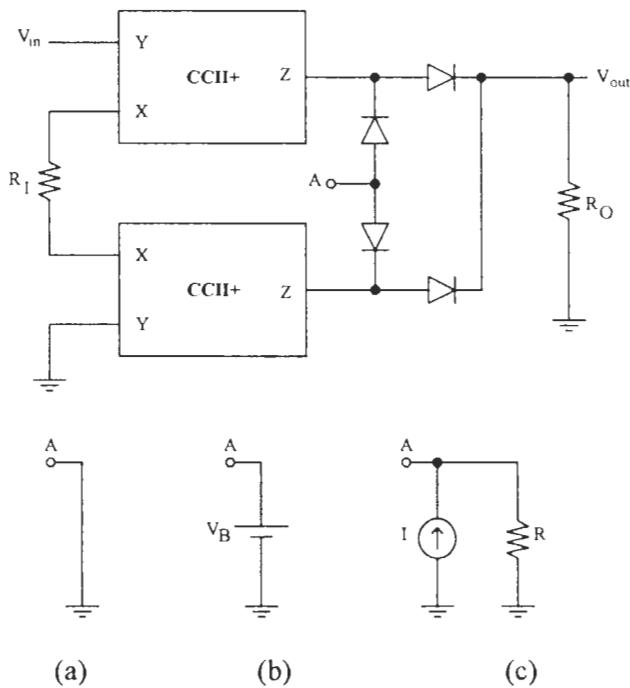

Recently, the full-wave rectifiers using current conveyors have been proposed. These full-wave rectifiers yield a main advantage in view of the high frequency operation. LTP Electronics Ltd. (1993) and Khan *et al.* (1995) originally proposed the same current conveyor full-wave rectifiers as shown in figure 1(a). This full-wave rectifier was developed to reduce the distortion due to the small-signal  $dV/dt$  limitation by Toumazou *et al.* (1994) with the addition of a DC voltage source as shown in figure 1(b). Hayatleh *et al.* (1994) further developed the full-wave rectifier to reduce the effect of temperature on the zero crossing performance by using a current source and a resistor in place of the voltage source as shown in figure 1(c). The above current conveyor full-wave rectifiers can apply to the differential input but cannot to the differential output.

In this work, the author will develop the current conveyor full-wave rectifier to be able to operate in the fully differential mode (be able to use with differential input and output). Moreover, the development yields the better points as follows.

- 1) Each of the above current conveyor full-wave rectifiers uses two passive resistors while the proposed full-wave rectifier uses all MOS structure. Hence, the proposed rectifier is more suitable for integrated circuit fabrication.

- 2) The above current conveyor full-wave rectifiers use commercial current conveyors, leading to the use of high supply voltage. The proposed rectifier uses the specially

designed current conveyors that use the lower supply voltage ( $\pm 2$  V), leading to lower power consumption.

3) Since current conveyors in the  $0.5 \mu\text{m}$  MOS technology are used in the proposed rectifier, the operation frequency of the proposed rectifier is higher.

## Proposed fully differential full-wave rectifier using current conveyors

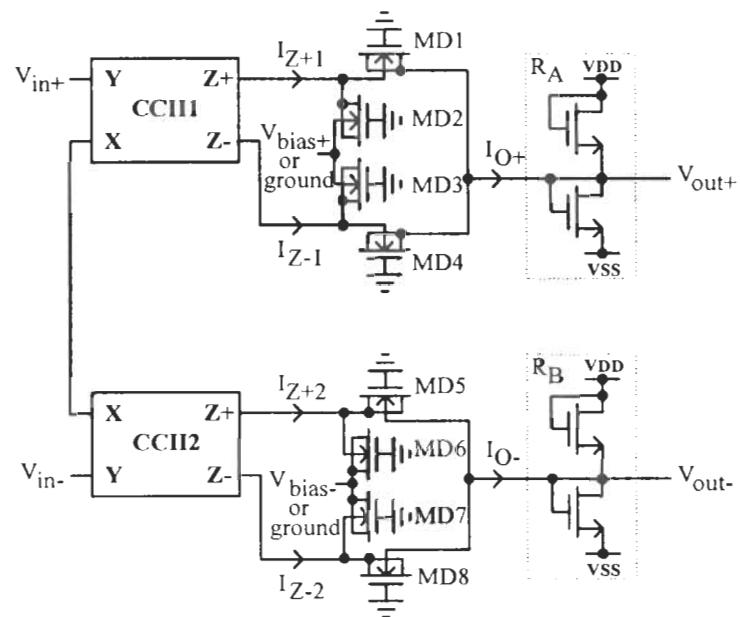

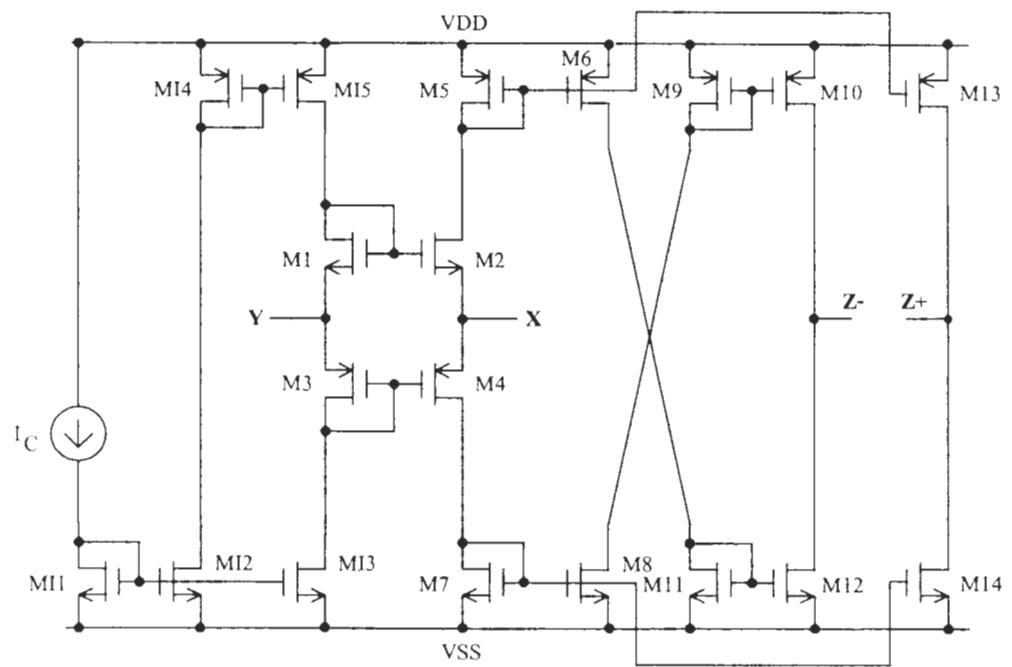

A proposed fully differential full-wave rectifier using current conveyors is shown in figure 2, which consists of two second-generation current conveyors (CCIIIs), one positive full-wave current rectifier, one negative full-wave current rectifier, and two MOS-resistors. The CMOS circuit of current conveyors [Bruun, 1993] is shown in figure 3. Each current conveyor in the proposed rectifier has four nodes, of which the relations of voltages and currents are given by

$$\left. \begin{array}{l} i_Y = 0 \\ v_X = v_Y \\ i_{Z+} = i_X \\ i_{Z-} = -i_X \end{array} \right\} \quad (1)$$

Comparing the proposed rectifier with the above rectifiers, one finds that a resistor connected between nodes X is not used for the proposed rectifier. This is compensated by using the low current  $I_C$  in the circuit of figure 3 to increase the resistance at nodes X ( $R_x$ ) of current conveyors [Bruun, 1993], normally, this resistance is very low. Another advantage of using the low current  $I_C$  is to consume low power.

Using (1) one finds that

$$i_{Z+1} = i_{Z-2} = -i_{Z-1} = -i_{Z+2} = \frac{V_m}{2R_x} \quad (2)$$

where  $V_m = V_{in+} - V_{in-}$ ; for a single mode application,  $V_{in-}$  has to be grounded.

Currents  $I_{Z+1}$  and  $I_{Z-1}$  are fed to the positive full-wave current rectifier that comprises four MOS-diodes, MD1 to MD4, [Monpapassorn *et al.* 2001] the drain and source together connected as cathode while the substrate as anode. When  $I_{Z+1}$  is positive,  $I_{Z-1}$  is negative,  $I_{Z+1}$  flows through

MD1 as  $I_{O+}$ ,  $I_{Z-1}$  is bypassed to ground by MD3. Inversely, when  $I_{Z+1}$  is negative,  $I_{Z-1}$  is positive, MD4 conducts  $I_{Z-1}$  as  $I_{O+}$ , MD2 conducts  $I_{Z+1}$  to ground. This operation leads to

$$\left. \begin{array}{l} V_m > 0; I_{O+} = \frac{V_m}{2R_x} \\ V_m < 0; I_{O+} = \frac{-V_m}{2R_x} \end{array} \right\} \quad (3)$$

Therefore  $I_{O+}$  is a positive full-wave current.

The inputs of the negative full-wave current rectifier (MD5 to MD8) are  $I_{Z+2}$  and  $I_{Z-2}$ . When  $I_{Z+2}$  is positive,  $I_{Z-2}$  is negative,  $I_{Z+2}$  is bypassed to ground by MD6,  $I_{Z-2}$  flows through MD8 as  $I_{O-}$ . In the opposite way, when  $I_{Z+2}$  is negative,  $I_{Z-2}$  is positive,  $I_{Z+2}$  flows through MD5 as  $I_{O-}$ ,  $I_{Z-2}$  is bypassed to ground by MD7. This operation yields

$$\left. \begin{array}{l} V_m > 0; I_{O-} = \frac{-V_m}{2R_x} \\ V_m < 0; I_{O-} = \frac{V_m}{2R_x} \end{array} \right\} \quad (4)$$

It is evident in (4) that  $I_{O-}$  is a negative full-wave current.

MOS-resistors [Wang, 1990],  $R_A$  and  $R_B$ , convert currents  $I_{O+}$  and  $I_{O-}$  to the positive full-wave voltage ( $V_{out+}$ ) and the negative full-wave voltage ( $V_{out-}$ ), respectively. The resistance of the MOS-resistor is given by

$$R = \frac{1}{2KV_{DT}} \quad (5)$$

where two NMOSs in the MOS resistor have the same characteristics;  $K = \mu C_{ox} W/L$ ,  $\mu$  is the mobility of carriers,  $C_{ox}$  is the gate capacitance per unit area,  $W$  and  $L$  are the channel width and length;  $V_{DT} = V_{DD} - V_T = -(V_{SS} + V_T)$ ,  $V_{DD} = -V_{SS}$ ,  $V_T$  is the threshold voltage.

If one sets the  $W/L$  ratios of NMOSs in two MOS-resistors to obtain  $R = 2R_x$ , exploiting (3) and (4), one can write  $V_{out+}$  as

$$\left. \begin{array}{l} V_m > 0; V_{out+} = V_m \\ V_m < 0; V_{out+} = -V_m \end{array} \right\} \quad (6)$$

and  $V_{out-}$  as

$$\left. \begin{array}{l} V_m > 0; V_{out-} = -V_m \\ V_m < 0; V_{out-} = V_m \end{array} \right\} \quad (7)$$

Equations, (6) and (7), show that  $V_{out+}$  and  $V_{out-}$  are a positive full-wave voltage and a negative full-wave voltage in the case of the single mode output (one output for use, another for ground). For the differential mode output, both outputs have to be together used, by using  $R = R_x$ , one obtains the positive full-wave rectification as

$$\left. \begin{array}{l} V_m > 0; V_{out+} - V_{out-} = V_m \\ V_m < 0; V_{out+} - V_{out-} = -V_m \end{array} \right\} \quad (8)$$

and the negative full-wave rectification as

$$\left. \begin{array}{l} V_m > 0; V_{out-} - V_{out+} = -V_m \\ V_m < 0; V_{out-} - V_{out+} = V_m \end{array} \right\} \quad (9)$$

which are the fully differential full-wave rectification.

## Simulation results

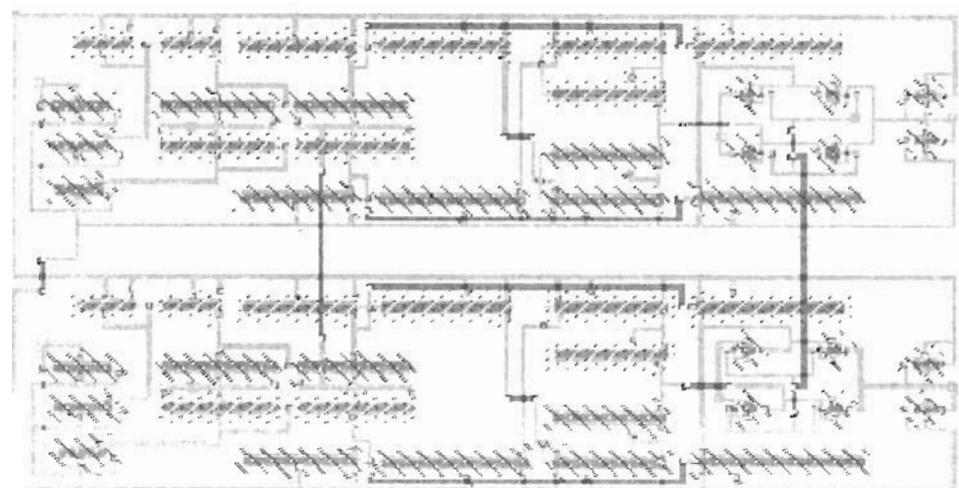

The author will verify a proposed fully differential full-wave rectifier by using its layout in a 0.5  $\mu\text{m}$  MOS technology of AMI as shown in figure 4 for simulation, the parasitic capacitance is included in simulation. The level 49 model of this technology is obtained through MOSIS, as shown in Table 1. The W/L ratios of M11 to M15 are based on 10  $\mu\text{m}$  / 1  $\mu\text{m}$  and those of M1 to M14 are based on 20  $\mu\text{m}$  / 1  $\mu\text{m}$ . A supply voltage used is  $\pm 2$  V. The constant current sources ( $I_C$ ) of current conveyors are 20  $\mu\text{A}$ . The bias voltages  $V_{bias+}$  and  $V_{bias-}$  are 0.7 V and  $-0.7$  V, respectively, these bias voltages make all MOS-diodes to turn-on all the time to reduce the on/off

transition problem at high frequency [Toumazou *et al.* 1994]. If the precise temperature stability is needed, the bias voltage sources[Monpapassorn *et al.* 2001] should be applied.

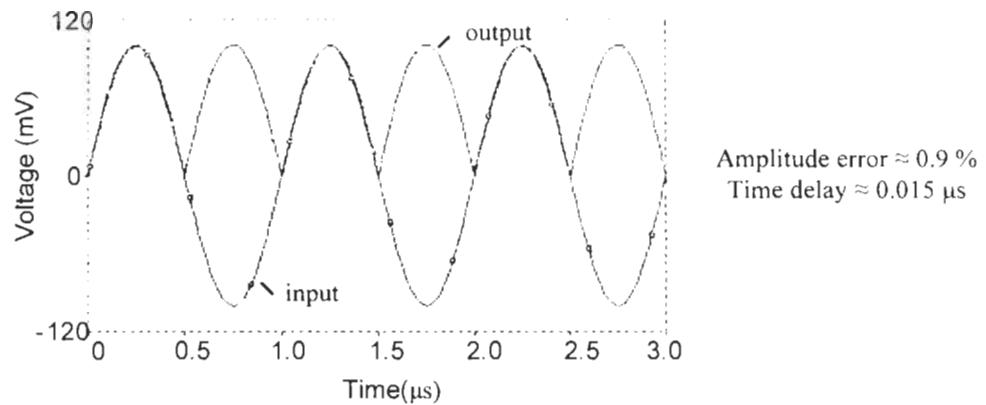

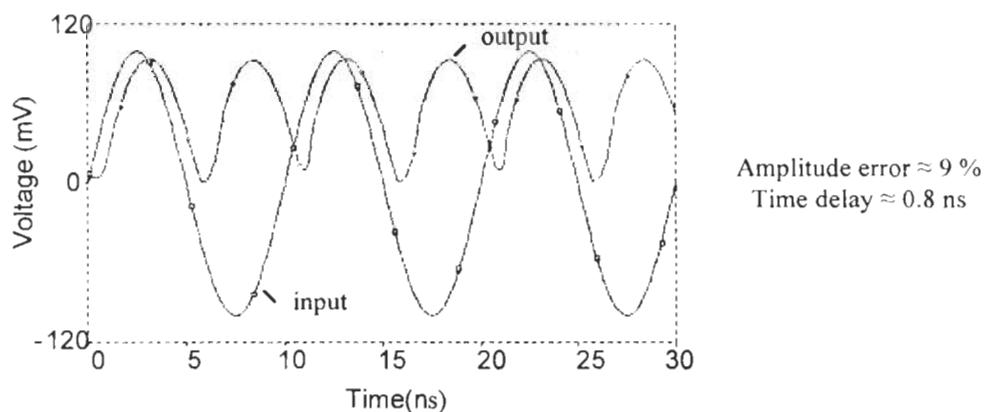

One feeds the sample 1 MHz and 100 MHz sine wave signals (100 mVpeak) at an input of the proposed full-wave rectifier operating in fully differential mode, then one gets the operation as shown in figure 5 and figure 6, respectively. One finds the error of an output voltage, compared with the absolute value of an input voltage, from figure 5 to be lower than 1 %, which results from carefully adjusting the W/L ratios of MOSSs in MOS-resistors to compensate the effect of  $R_x$ . In figure 5, the output signal is evidently delayed from the input signal due to the effect of the equivalent capacitors of the circuit. In addition, the amplitude of the output signal decreases because of the decrement of the transferring gains of current conveyors at high frequency. The input and output delay must be considered in use and the input and output amplitude error can be compensated by adjusting the W/L ratios of MOSSs of  $R_A$  and  $R_B$  to get the suitable resistance. The power consumption in this simulation from a reported file of the SPICE program is not more than 1.2 mW, which is much lower than that of the above current conveyor full-wave rectifiers.

## Conclusion

In this work, the author has reported the design and simulation of a fully differential full-wave rectifier using current conveyors. The advantages of the proposed full-wave rectifier, compared with the previously proposed current conveyor full-wave rectifiers, are using lower supply voltage, consuming lower power, yielding wider operation frequency range, forming all MOS structure, and applying both single and differential modes. It should be noted on the use of the proposed rectifier that it is suitable for a high impedance load. If a low impedance load is applied, the proposed rectifier needs the buffers at outputs.

## References

LTP Electronics Ltd. 1993. **CCII01 current-conveyor data sheet**. Oxford.

Khan, A.A, Abou El-ele, M., and Al-Turaigi, M.A. 1995. Current-mode precision rectification. **International Journal of Electronics**. 79: 853-859.

Toumazou, C., Lidgey, F.J., and Chattong, S. 1994. High frequency current conveyor precision full-wave rectifier. **Electronics letters**. 30: 745-746.

Hayatleh, K., Porta, S., and Lidgey, F.J. 1994. Temperature independent current conveyor precision rectifier. **Electronics letters**. 30: 2091-2093.

Bruun, E. 1993. CMOS high speed, high precision current conveyor and current feedback amplifier structures. *International Journal of Electronics*. 74: 93-100.

Monpapassorn, A., Dejhan, K., and Cheevasuvit, F. 2001. CMOS dual output current mode half-wave rectifier. *International Journal of Electronics*. 88:1073-1084.

Wang, Z. 1990. 2-MOSFET transresistor with extremely low distortion for output reaching supply voltages. *Electronics Letters*.26: 951-952.

```

.MODEL CMOSN NMOS LEVEL= 49

+VERSION = 3.1 TNOM=27 TOX=1.39E-8

+XJ=1.5E-7 NCH=1.7E17 VTH0=0.6696061

+K1=0.8351612 K2=-0.0839158 K3=23.1023856

+K3B=-7.6841108 W0=1E-8 NLX=1E-9

+DVT0W=0 DVT1W=0 DVT2W=0

+DVT0=2.9047241 DVT1=0.4302695 DVT2=-0.134857

+U0=458.439679 UA=1E-13 UB=1.485499E-18

+UC=1.629939E-11 VSAT=1.643993E5 A0=0.6103537

+AGS=0.1194608 B0=2.674756E-6 B1=5E-6

+KETA=-2.640681E-3 A1=8.219585E-5 A2=0.3564792

+RDSW=1.387108E3 PRWG=0.0299916 PRWB=0.0363981

+WR=1 WINT=2.472348E-7 LINT=3.597605E-8

+XL=0 XW=0 DWG=-1.287163E-8

+DWB=5.306586E-8 VOFF=0 NFACTOR=0.8365585

+CIT=0 CDSC=2.4E-4 CDSCD=0

+CDSCB=0 ETA0=0.0246738 ETAB=-1.406123E-3

+DSUB=0.2543458 PCLM=2.5945188 PDIBLC1=-0.4282336

+PDIBLC2=2.311743E-3 PDIBLCB=-0.0272914 DROUT=0.7283566

+PSCBE1=5.598623E8 PSCBE2=5.461645E-5 PVAG=0

+DELTA=0.01 RSH=81.8 MOBMOD=1

+PRT=8.621 UTE=-1 KT1=-0.2501

+KT1L=-2.58E-9 KT2=0 UA1=5.4E-10

+UB1=-4.8E-19 UC1=-7.5E-11 AT=1E5

+WL=0 WLN=1 WW=0

```

```

+WWN=1 WWL=0 LL=0

+LLN=1 LW=0 LWN=1

+LWL=0 CAPMOD=2 XPART=0.5

+CGDO=2E-10 CGSO=2E-10 CGBO=1E-9

+CJ=4.197772E-4 PB=0.99 MJ=0.4515044

+CJSW=3.242724E-10 PBSW=0.1 MJSW=0.1153991

+CISWG=1.64E-10 PBSWG=0.1 MJSWG=0.1153991

+CF=0 PVTH0=0.0585501 PRDSW=133.285505

+PK2=-0.0299638 WKETA=-0.0248758 LKETA=1.173187E-3

+AF=1 KF=0

.MODEL CMOSP PMOS LEVEL= 49

+VERSION=3.1 TNOM=27 TOX=1.39E-8

+XJ=1.5E-7 NCH=1.7E17 VTH0=-0.9214347

+K1=0.5553722 K2=8.763328E-3 K3=6.3063558

+K3B=-0.6487362 W0=1.280703E-8 NLX=2.593997E-8

+DVT0W=0 DVT1W=0 DVT2W=0

+DVT0=2.5131165 DVT1=0.5480536 DVT2=-0.1186489

+U0=212.0166131 UA=2.807115E-9 UB=1E-21

+UC=-5.82128E-11 VSAT=1.713601E5 A0=0.8430019

+AGS=0.1328608 B0=7.117912E-7 B1=5E-6

+KETA=-3.674859E-3 A1=4.77502E-5 A2=0.3

+RDSW=2.837206E3 PRWG=-0.0363908 PRWB=-1.016722E-5

+WR=1 WINT=2.838038E-7 LINT=5.528807E-8

+XI=0 XW=0 DWG=-1.606385E-8

+DWB=2.266386E-8 VOFF=-0.0558512 NFACTOR=0.9342488

+CIT=0 CDSC=2.4E-4 CDSCD=0

+CDSCB=0 ETA0=0.3251882 ETAB=-0.0580325

+DSUB=1 PCLM=2.2409567 PDIBLC1=0.0411445

+PDIBLC2=3.355575E-3 PDIBLCB=-0.0551797 DROUT=0.2036901

+PSCBE1=6.44809E9 PSCBE2=6.300848E-10 PVAG=0

+DELTa=0.01 RSII=101.6 MOBMOD=1

```

```

+PRT=59.494 UTE=-1 KT1=-0.2942

+KT1L=1.68E-9 KT2=0 UA1=4.5E-9

+UB1=-6.3E-18 UC1=-1E-10 AT=1E3

+WL=0 WLN=1 WW=0

+WWN=1 WWL=0 LL=0

+LLN=1 LW=0 LWN=1

+LWL=0 CAPMOD=2 XPART=0.5

+CGDO=2.9E-10 CGSO=2.9E-10 CGBO=1E-9

+CJ=7.235528E-4 PB=0.9527355 MJ=0.4955293

+CJSW=2.692786E-10 PBSW=0.99 MJSW=0.2958392

+CJSWG=6.4E-11 PBSWG=0.99 MJSWG=0.2958392

+CF=0 PVTH0=5.98016E-3 PRDSW=14.8598424

+PK2=3.73981E-3 WKETA=5.292165E-3 LKETA=-4.205905E-3

+AF=1 KF=0

```

**Table 1** Model used in simulation.

Figure 1 Current conveyor rectifiers: (a) proposed by LTP Electronics Ltd. and Khan et al., (b) proposed by Toumazou et al., (c) proposed by Hayatleh et al..

Figure 2 Proposed fully differential full-wave rectifier.

Figure 3 Circuit of CCII's in figure 2.

Figure 4 Layout of the proposed fully differential full-wave rectifier.

**Figure 5** Operation of the proposed rectifier at the frequency of 1 MHz.

**Figure 6** Operation of the proposed rectifier at the frequency of 100 MHz.